産業技術総合研究所(産総研)は,内閣府 総合科学技術・イノベーション会議(CSTI)が主導する革新的研究開発推進プログラム(ImPACT)の一環として,次世代の不揮発性メモリーである磁気ランダムアクセスメモリ(MRAM)の3次元積層プロセス技術を開発した(ニュースリリース)。

産業技術総合研究所(産総研)は,内閣府 総合科学技術・イノベーション会議(CSTI)が主導する革新的研究開発推進プログラム(ImPACT)の一環として,次世代の不揮発性メモリーである磁気ランダムアクセスメモリ(MRAM)の3次元積層プロセス技術を開発した(ニュースリリース)。

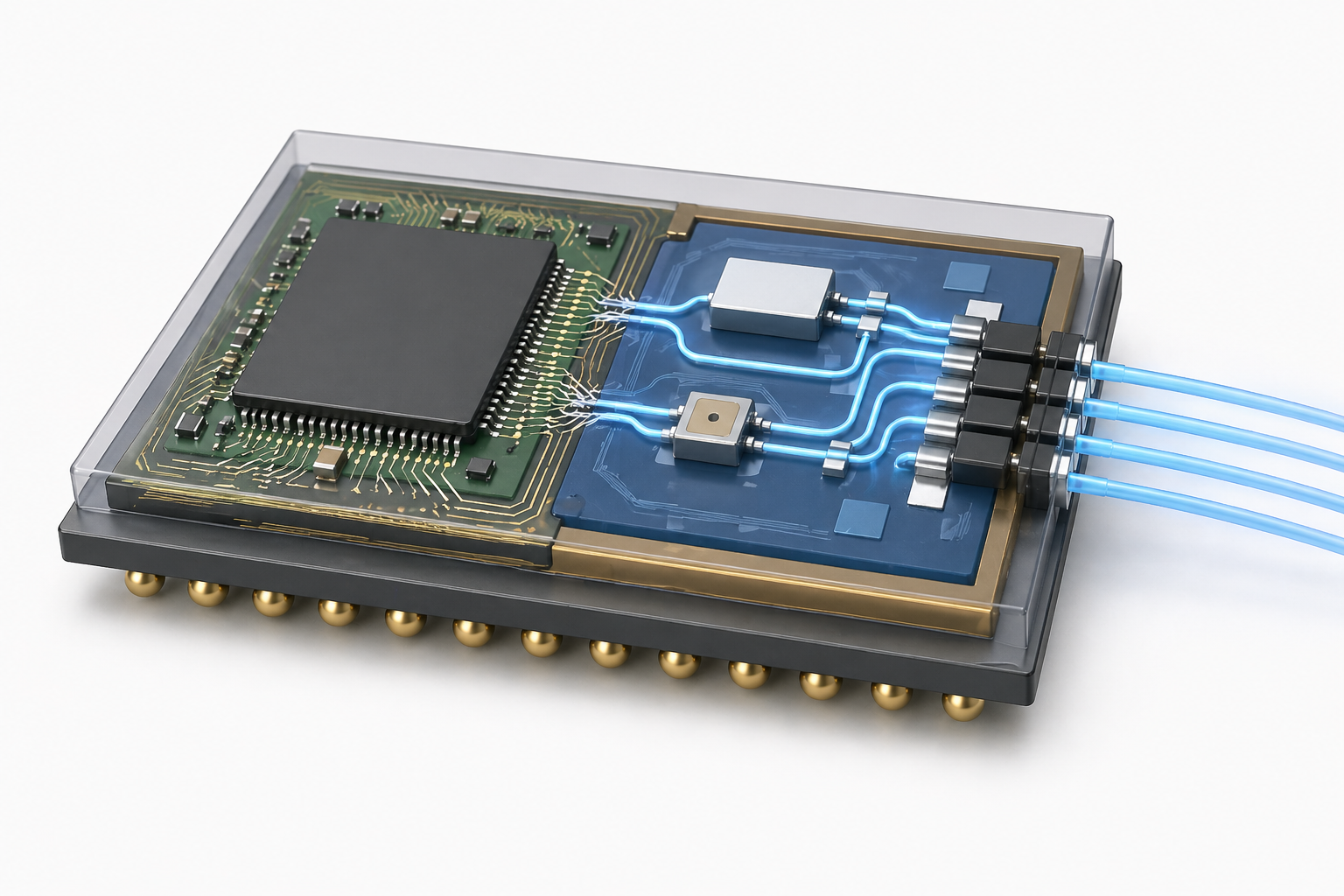

MRAMは垂直磁化TMR素子をベースとする記録ビットと,ビット選択に用いる半導体トランジスタ(CMOS),金属配線(通常,多結晶の銅配線)からなり,通常,垂直磁化TMR素子薄膜(TMR薄膜)は,CMOS形成後に金属配線上に直接形成される(逐次積層)。

MRAMの大容量化には,原子レベルの不均一性や凹凸によるTMR薄膜のバラツキ抑制や,材料の選択が重要だが,多結晶銅配線上へのTMR薄膜形成ではバラツキ抑制や材料の選択肢には限界がある。

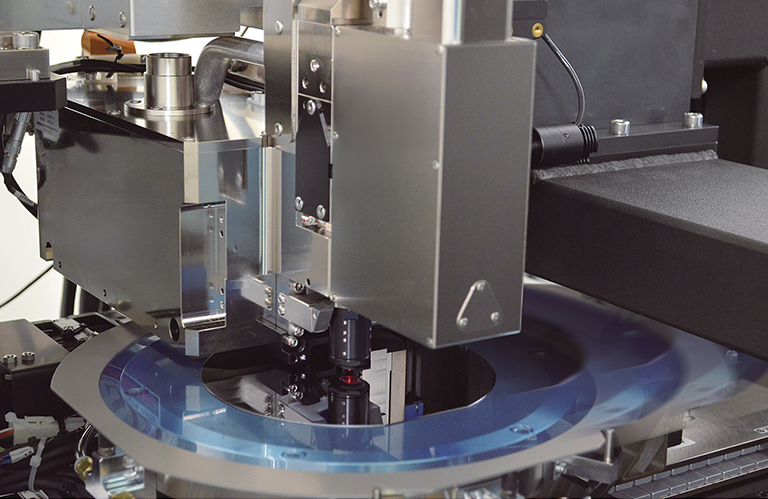

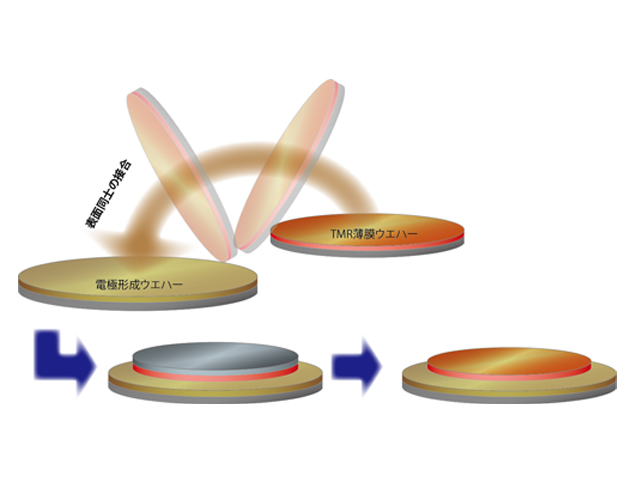

今回,CMOS形成ウエハー(今回は銅電極形成ウエハーで代用)とTMR薄膜ウエハーを別体形成した後に圧着して接合する,3次元積層プロセス技術によるTMR素子の作製に世界で初めて成功した。

ウエハー上に銅電極層,タンタル接合層,多結晶TMR薄膜層の順に形成された3次元積層試料に微細加工を行ない,サイズが28nmから65nmのMRAMデバイスを作製し,動作を確認した。比較のために,3次元積層プロセスを行なわないTMR薄膜を用いたMRAMデバイスも作製して動作確認を行なった。

その結果,3次元積層プロセスを経た後のMRAMデバイスは,読出性能・書込性能は全く劣化せず,STT-MRAMで重要な性能指標となる「データ書き込み効率」は2に達し,世界トップクラスの性能を維持していた。

この技術開発によりウエハーの別体形成が可能になったことで,薄膜のバラツキが極めて小さく,高性能材料候補の選択肢が広い単結晶材料をMRAM製造に用いる目途が立った。これにより,MRAMの飛躍的な大容量化と高性能化につながるとしている。