東京大学の研究グループは、誤り耐性型量子コンピュータの性能を左右する規模と計算速度のジレンマを解消する新しい理論を確立した(ニュースリリース)。

量子コンピュータは通常のコンピュータと比較してある種の計算問題を高速に解く能力が期待されているが、その最小単位である量子ビットはノイズに弱く、エラーが発生しやすいという根本的な問題がある。そのため、大規模な計算には、発生したエラーを計算途中で訂正しながら処理を進める「誤り耐性量子計算」が不可欠となっている。

誤り耐性量子計算では、量子エラー訂正符号という技術を用いて、計算に使う量子ビットを、ノイズの影響を受けやすい実際のデバイスに並べた多数の物理量子ビットの組み合わせとして構成することでエラーから保護する。

このとき、量子コンピュータの規模に直結する、1つの論理量子ビットを保護するために必要な物理量子ビットの数と、計算速度に直結する、誤り耐性化の一連の処理によって生じる計算の遅延の比率を可能な限り小さくすることが重要。

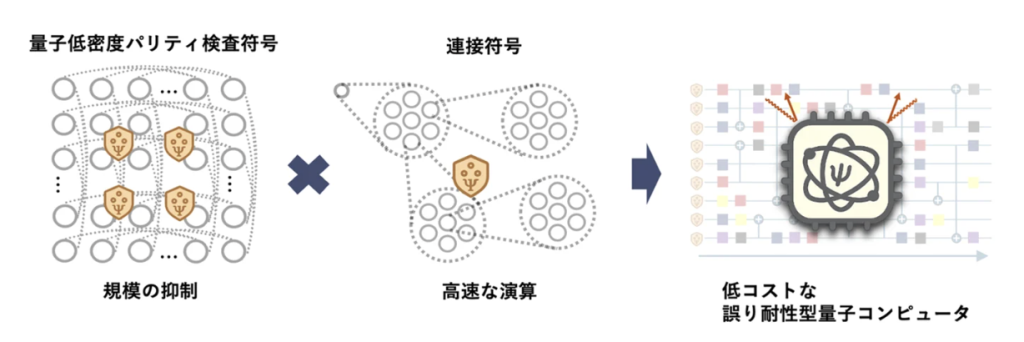

この規模と計算速度は、使用する量子エラー訂正符号に左右される。例えば、近年注目される量子低密度パリティ検査符号は、少ない物理量子ビットで多くの情報を保護できる符号だが、その複雑な構造から計算を行なうのが難しいという弱点がある。

一方、古くから知られる連接符号は、構造のシンプルさから計算の実行速度は高いものの、情報を保護するためには多くの物理量子ビットを必要とする。このように規模の増大と計算速度の低下は、両方を同時に理想的なレベルで抑えることが困難だった。

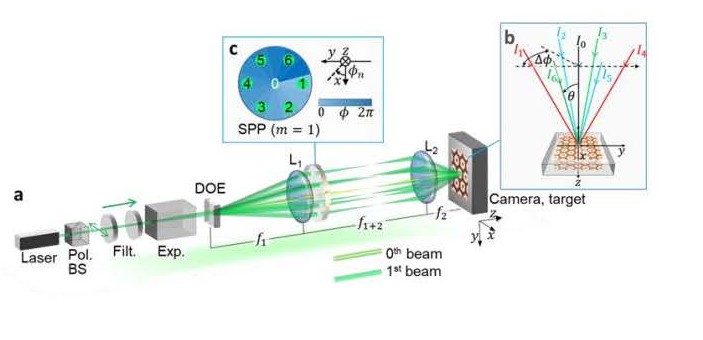

そこで研究グループは、この2種類の量子エラー訂正符号を適材適所で活用するハイブリッド方式を採用した。具体的には、情報の保持効率に優れた量子低密度パリティ検査符号を用い、苦手とする計算については、実行を加速する効果を持つ補助的な量子の状態を、高速な連接符号を用いて生成するという役割分担。

この方式の性能解析にあたっての主要課題は、動作原理の異なる2つの符号を組み合わせた複雑な回路において、エラーの伝播と計算結果への影響を統一的に評価することだった。そのために、使用する符号の種類を問わず、巨大な回路を機能ごとの部品に分割し、各部分のエラー特性を個別に評価することで回路全体のエラー確率を厳密に導き出す「部分回路縮約」という新たな解析手法を開発した。

その結果、今回の研究で生まれた誤り耐性量子計算の方式が、規模の増大を大幅に抑制しつつ、計算速度の低下を連接符号と同レベルに留められることを厳密に証明した。

研究グループは、この成果は、誤り耐性型量子コンピュータ実現に向けた長年の課題を克服し、その開発に不可欠な理論基盤を提供するものだとしている。