1.はじめに

再帰型ニューラルネットワーク(RNN:Recurrent Neural Network)は,自然言語処理や音声認識,金融市場予測などの時系列データを用いたアプリケーション処理に利用されている。RNNはネットワークに内在する再帰構造により時系列依存性を捉えることが可能なため,時系列タスクの処理に適している。近年では, Universal Transformers(UT)やDeep Equilibrium Model(DEQ)の登場により,逐次実行モデルの性能が更に向上している。UT は,再帰構造を用いたアテンション機構により,長距離の依存関係を効率的に把握することができる。また,DEQ では再帰処理を繰り返すことで出力が一定値に収束させ,均衡点そのものを学習することで,勾配消失問題に対処し,さらなる深層ネットワーク構造を可能にしている。これらの提案は,複雑な時系列モデルにおける再帰構造の重要性を示唆している。

RNNの応用分野である異常検知,音声認識,金融市場予測などのタスクでは,リアルタイム性能がますます重要になるにつれ,低レイテンシでの推論の必要性が高まっている。株式市場での不正検知や大型ハドロン衝突型加速器におけるイベント検知では,とくに高速な処理が要求される。たとえば,株式市場での不正検知には,一度の取引に対して113 μs以下の応答が要求される。

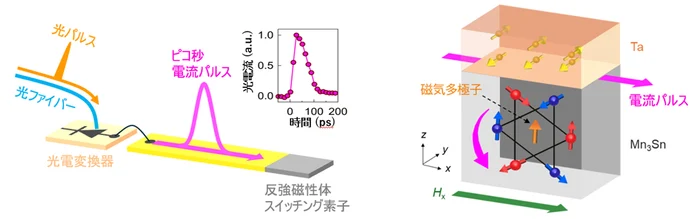

しかしながら,一般的なCMOS汎用プロセッサにて理論ピーク性能を640GFLOPS と想定すると,推論処理に6.25 msを要する。CMOSトランジスタの微細化が物理的限界に近づいている現在,電気回路は主にRC遅延によるレイテンシのボトルネックに直面している。このため,マイクロ秒やナノ秒レベルのレイテンシを実現できる,CMOSトランジスタの代替となる新奇デバイスの必要性が高まっている。

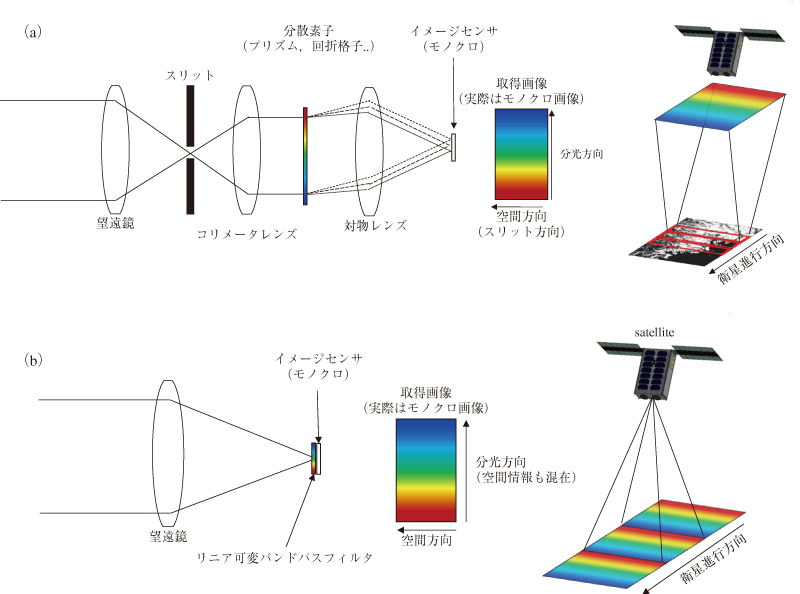

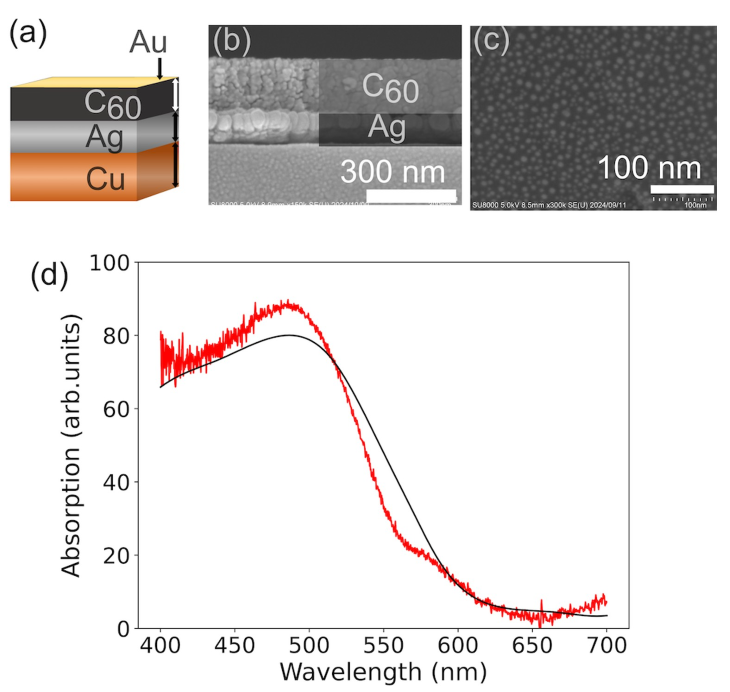

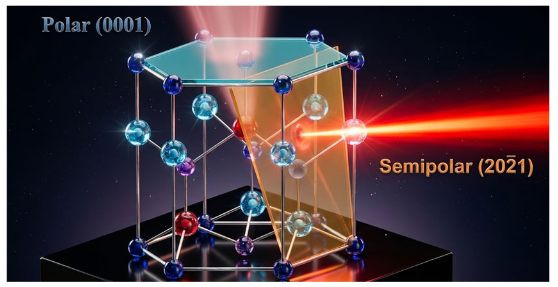

そこで,CMOS技術の限界を克服する方法の一つとして,光コンピューティングが有望視されている。光子は,電場や磁場の影響を受けにくいという性質を持つため,電子配線で生じる寄生抵抗や浮遊容量に依存することなく光の速度での信号伝達が可能となる。これまで,光デバイスの特長である高速性,低消費電力性という恩恵を最大化するべく,畳み込みニューラルネットワークに代表されるFFNN(Feedforward Neural Network)の推論を高速に行うアクセラレータに焦点が当てられ,計算機システムレベルでその優位性が示されてきた。

しかしながら,既存の光アクセラレータは非線形演算やメモリ機能を電気的処理に依存しているため,大幅なレイテンシとエネルギーのオーバーヘッドが生じる。この課題は,時系列処理に連続的なフィードバックを必要とするRNNのような再帰構造を持つネットワークに置いて特に顕著である。たとえば,マイクロリング共振器(MRR: Microring Resonator)をベースとするAlbireoや,マハツェンダー干渉計(MZI:Mach-Zehnder Interferometer)を使用したPIXELなどでは,行列演算単体でみると極めて高い効率性を有する。一方で,システムレベルでは光-電気(O/E)変換やアナログ-デジタル(A/D)変換のオーバーヘッドが大きな課題となる。さらに,再帰構造を持つネットワークを処理する場合,このオーバーヘッドがさらに増大するため,光の持つ高速性,低消費電力性を十分に発揮できず,光アクセラレータの最大の利点を失う可能性がある。

これらは光コンピューティング共通の課題であり,“光を活用する利点がドメイン間の変換コストを凌駕する”場合にのみ,計算機としての優位性が生じるのである。本記事では,RNNに最適化された新しいフォトニックアーキテクチャを紹介する。この設計により,非線形処理における電気回路への依存が排除され,変換オーバーヘッドが削減されるため,より効率的で低レイテンシのRNN実行が可能になる。

【月刊OPTRONICS掲載記事】続きを読みたい方は下記のリンクより月刊誌をご購入ください。

本号の購入はこちら