東京工業大学と共同研究企業は,”Pillar-Suspended Bridge(PSB)”と呼ぶ技術を用いたチップレット集積技術を開発した。これは,今後の大規模なチップレット集積に求められる,広帯域のチップ間接属性能,チップレット集積規模の拡大といった要求を最小限の構成と製造プロセスで実現するもの(ニュースリリース)。

東京工業大学と共同研究企業は,”Pillar-Suspended Bridge(PSB)”と呼ぶ技術を用いたチップレット集積技術を開発した。これは,今後の大規模なチップレット集積に求められる,広帯域のチップ間接属性能,チップレット集積規模の拡大といった要求を最小限の構成と製造プロセスで実現するもの(ニュースリリース)。

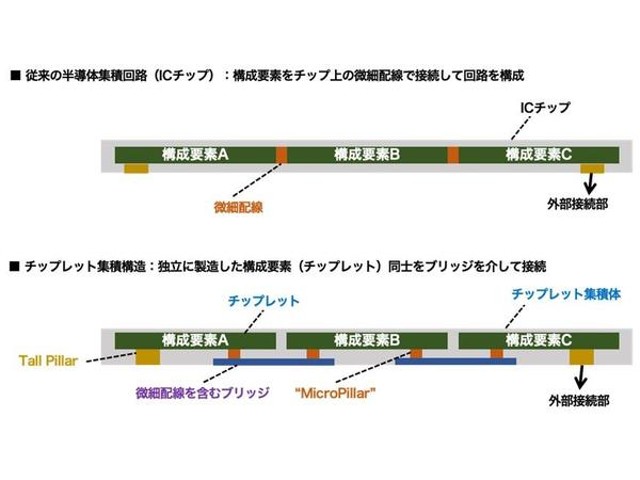

微細化に変わる集積規模拡大,性能向上/消費電力低減の新しい進化軸として,チップレット集積技術が注目を集めている。これは,主要なシステムを,従来の半導体実装技術に比べて密に結合された集積回路チップの集合体により構成するもので,半導体ウエハー/チップの物理的/製造技術的なディメンジョンを超え,かつ異なる機能・構造のものを大規模に集積するもの。これにより,従来の半導体集積回路技術では実現できなかった,異種構造集積による性能向上や集積規模のスケーラビリティを提供することが可能になる。

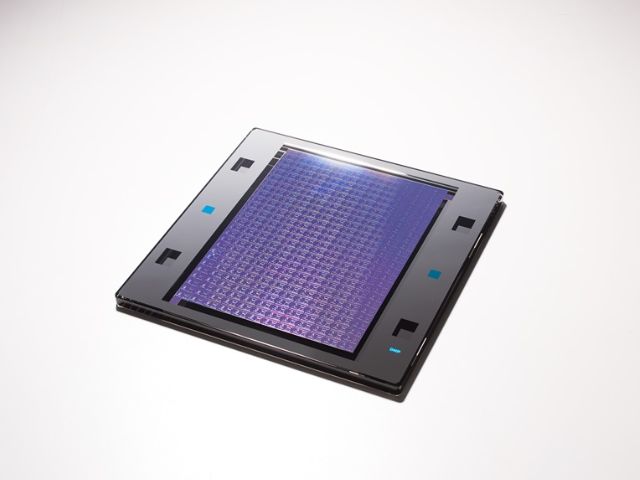

今回の研究はこうしたの背景と課題に鑑み,最小要素のチップレット集積構造/プロセスとして”Pillar-Suspended Bridge(PSB)” 技術を考案,コンセプト実証試作を行ない,その実現性を立証した。

チップレットとシリコン・ブリッジの接続部には”MicroPillar”と呼ぶ柱状金属のみが介在している。チップレット集積体はブリッジと共にモールド樹脂封止されており,シリコン・ブリッジ側のモールドを貫通する”Tall Pillar”により外部電極に接続する。

この構造により,チップレット/ブリッジの最小限の接続構造によるチップ間接続密度や電気特性の向上,外部接続配線の高周波特性や放熱性能の改善が可能。また,ブリッジの配線の種類が選択可能であることや,集積規模拡大時の歩留まりの問題がなく(Known Good Bridge),集積モジュールのサイズや製造単位を大型パネルなどへ拡大できるという利点があるという。

この構造は,製造工程における①All Chip-lastプロセスによる高い接合精度と製造工程中のダイ・シフト(モールド封止の際チップが動いてしまう現象)の抑制,②線膨張(Coefficient of Thermal Expansion:CTE)の整合した接合プロセスにより実現した。

SB構造はブリッジ接続によるチップレット集積に関してシンプルで合理的な構造を有しており,これにFan-Out機能を有する配線層(例えばRDL Interposer)を接続することで,理想的なチップレット集積パッケージや,大規模なチップレット集積システムを構成することができる。

研究グループは,チップレット集積技術はシステム性能向上のための新しい進化軸として期待されるとしている。また,チップレット集積プラットフォーム・コンソーシアムを2022年10月1日に設立している。