京都大学の研究グループは,SiC半導体で問題になっていた欠陥を大幅に低減し,実用的な構造でSiCトランジスタの性能を6倍以上向上した(ニュースリリース)。

京都大学の研究グループは,SiC半導体で問題になっていた欠陥を大幅に低減し,実用的な構造でSiCトランジスタの性能を6倍以上向上した(ニュースリリース)。

半導体パワーデバイスに主に使われているSiは理論限界に達しつつあり,新しい半導体材料が求められている。

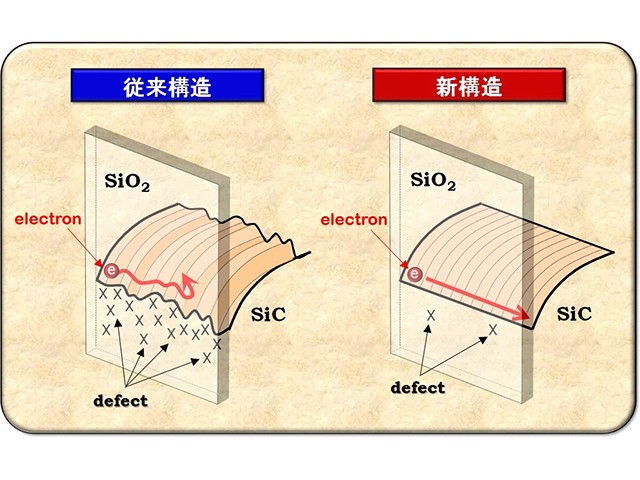

そこでSiCの研究開発競争が熾烈になっているが,SiCトランジスタの酸化膜とSiCの界面にある多数の欠陥により,SiC本来の性能を発揮できない状況が20年以上続いている。

研究グループは,「SiC を酸化せずに良質の酸化膜を形成すること」に着目し,昨年,①高温の水素処理によりSiC表面を清浄化,②(酸化膜(SiO2薄膜)を酸化ではなく堆積法により形成,③一酸化窒素による界面窒化,の3つの技術を組み合わせることによって,界面欠陥を大幅に低減し,SiCトランジスタの性能を2倍に向上できることを報告した。

今回,この研究を発展させ,実用上重要なトランジスタ構造(結晶面,不純物密度)で画期的な性能向上を達成したポイントは以下の通り。

①SiCトランジスタの高性能化には,「トレンチ型」MOSFETが有望であることがわかっている。トレンチ型MOSFETでは,心臓部である酸化膜/SiC界面がSiC ウエハー表面(Si面)ではなく,ウエハー表面に直交する(「A 面」,「M 面」)に形成される。今回,このA面およびM面基板を準備し,上記手法でSiC MOSFETを作製した結果,従来のSi面上MOSFET(従来の酸化膜形成法を採用)に比べ6~7倍の性能向上を達成した。

②さらに,実際に製造されるSiCトランジスタでは,トランジスタの耐電圧の増大や信頼性向上のために,比較的高濃度の不純物(アクセプタ型不純物:アルミニウム)を添加したp型領域の上にMOS構造を形成する必要がある。今回,製造に用いられる高濃度p型SiCを用いてA面,M面上MOSFETを作製した結果,従来技術によるA面,M面上MOSFETに比べて6~80倍の性能向上を達成した。

この手法により形成した酸化膜とA面,M面SiCの界面欠陥の密度が,従来手法構造に比べて大幅に低減したことは確認できており,これがトランジスタの性能向上に直結したとみている。

また,高濃度にアルミニウムを添加したSiCの場合にこの手法の効果が一層大きくなるのは,酸化膜とSiC界面の平坦性が優れており,電子の散乱(走行の阻害)が著しく減少したためだとする。

研究グループは,この成果を電力用SiCトランジスタ(MOSFET)に適用すれば,チップ面積縮小による低コスト化と信頼性の向上を達成できるとしている。