電気通信大学の研究グループは,従来よりも10倍以上の高い密度で,かつ細線直径の標準偏差が10%以下の高均一なInAs(インジウムヒ素)量子ナノワイヤー(量子細線)を Si(シリコン)基板上に作製する技術を開発した(ニュースリリース)。

高機能な次世代デバイスに量子ナノワイヤーを応用するには,量子ナノワイヤーのサイズ制御や高密度化などの基盤技術が必要になる。しかしながら,従来の多くのナノワイヤー成長では,サイズが直径100nm~数百nmと比較的大きいものが多く,電子の量子閉じ込め効果が十分ではなかった。

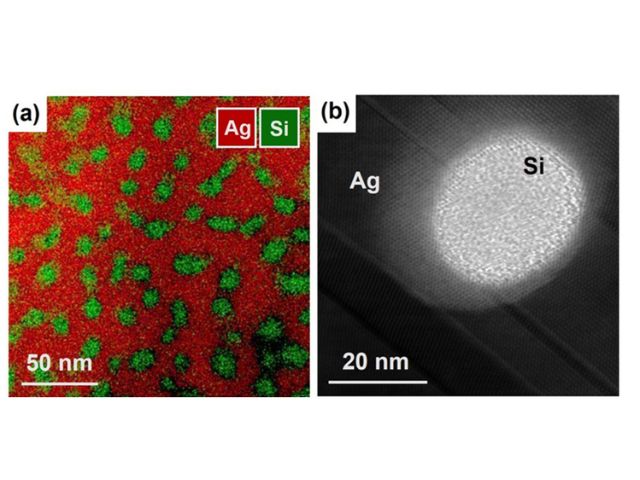

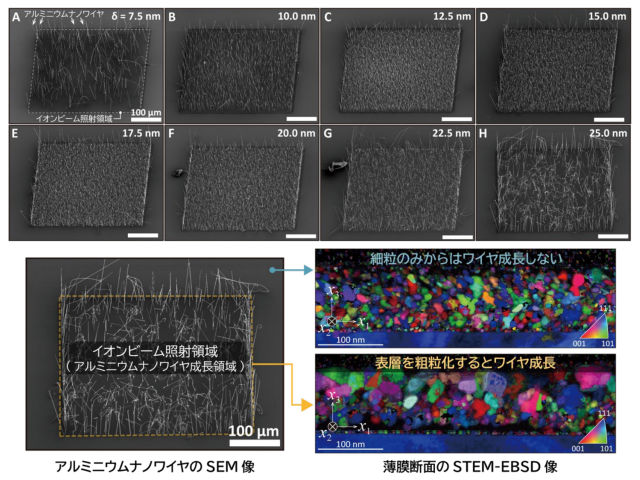

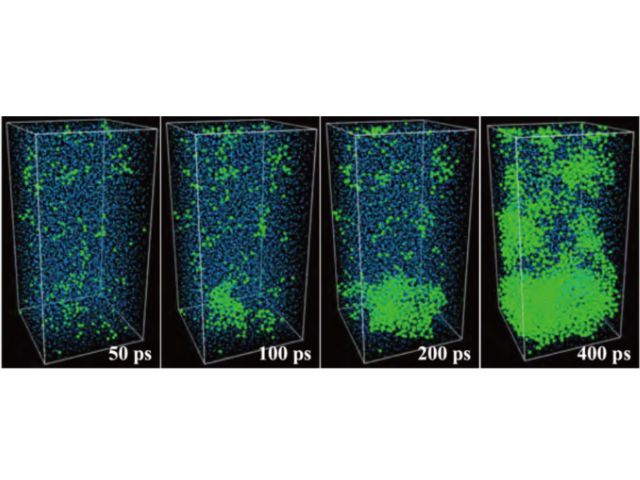

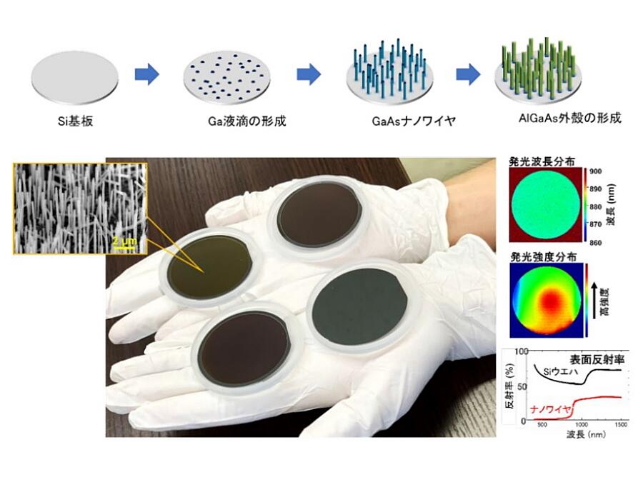

研究グループは,今回,高密度で高均一な量子ナノワイヤー構造の作製に向けて,MBE法を使い,Si基板表面の酸化膜にGaナノ液滴を堆積し,基板加熱による反応過程によってnmサイズのピンホールを形成する手法を用いた。

この際,Ga液滴の供給量や反応温度,Si酸化膜表面の清浄化が重要になる。特に酸化膜表面の清浄化については,電子線の照射による表面への炭素などの吸着がピンホールの形成を阻害することが分かった。このことから,表面構造の観察に用いる電子線照射や,表面パターン形成のための電子線照射などのプロセスは避ける必要があることを明らかにした。

このようにしてSi酸化膜に高品質なピンホールを作製した上で,ピンホール底のSi基板結晶からInAs単結晶核を形成し,高さ方向の成長が促進された六方晶(ウルツ鉱構造)のInAsナノワイヤーを高密度かつ高均一に形成した。

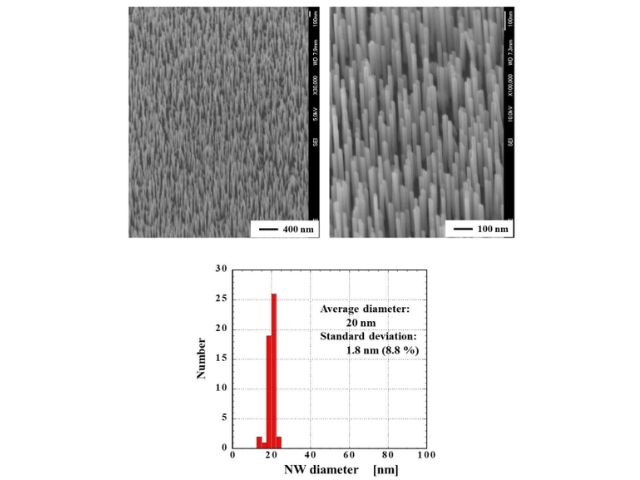

結晶成長実験では,面内密度が1~2×1010cm-2のInAsナノワイヤーが再現性高く得られ,従来のナノワイヤーの10倍から100倍の高い密度で形成できた。また,ナノワイヤー構造以外の堆積物や多結晶粒の形成も抑制できることから,直径30nm以下の細いナノワイヤー構造を制御性高く作製することが可能になり,これによって量子サイズ効果を発現する量子ナノワイヤーを標準偏差8.8%と高均一に作製することに成功した。

研究グループは,高密度で高均一な半導体量子ナノワイヤーがSi基板上に作製できたことで,Si基板に集積する次世代の縦型トランジスタやメモリーのほか,量子ドット構造を内蔵した量子細線レーザーや量子構造太陽電池,量子ナノセンサーなどの量子デバイスの高機能化や超集積化が可能になるとしている。