東京大学の研究グループは,半導体製造において大部分を占めるフォトマスクの開発コストを1/40に削減しつつ,低電力性能を両立した新規ストラクチャードASIC型AIプロセッサを開発した(ニュースリリース)。

スマートウォッチやAR/VR機器においてもAI機能の搭載が期待されているが,こうしたIoT機器は小型軽量動作を追求するためバッテリ駆動であり,かつ安価であることが求められる。これまで低電力動作を追求するためAIプロセッサが世界中で研究開発されているが,いずれもフォトマスク開発にかかる10億円単位の開発コストが高い障壁となりIoTデバイスへの採用が困難だった。

低電力性能を追求するほどタスクに特化するため汎用性がなくなり,半導体の設計データであるフォトマスクを使い回すことができなくなる。フォトマスクの開発製造は非常に高額であり,この開発コストを回収するためにはチップ単価が極めて高額になることから,安価なデバイスの実現が難しいという問題があった。

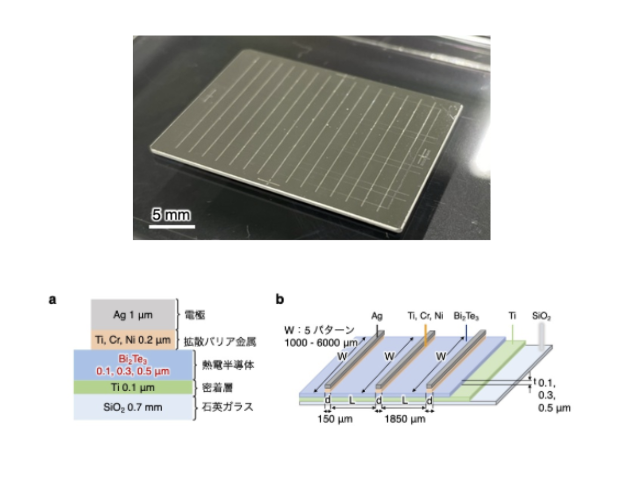

研究グループは,低電力動作と低コストを両立するため,ストラクチャードASIC方式の新規AIプロセッサを開発した。演算回路と配線をあらかじめ実装したチップを上層配線の途中まで製造しておき,VIA1 層のみで特定のAI処理に応じたAIプロセッサ回路を構成するビアプログラマブルニューロンアレー技術を開発した。

AIプロセッサの製造に必要なフォトマスク枚数をVIA層1枚に減らし低コスト化を実現した。実現にあたっての技術課題は巨大な実装面積。深層ニューラルネットワークを布線論理方式で実装するため,実装する信号配線が膨大になり広大なチップ面積が必要となっていた。

従来方式では半導体集積回路として製造可能な限界面積を大幅に超過していたため,実現できなかった。そこで研究グループは新たに回路と信号配線を時分割で再利用し回路面積を削減する,ビットニューロン順次回路技術を開発した。

さらに深層ニューラルネットワークの重み係数を16ビットから3値に削減しながらも精度を保つ,関数選択的非線形ニューラルネットワーク(FS-NNN)技術も開発した。重み係数を16ビットから3値にすることで必要な信号配線本数を削減している。

これらの技術を組み合わせた結果,信号配線本数を1/1024に削減し省面積化を実現,10mm2以下とIoT用途として十分小さな回路面積でストラクチャードASICによるAI機能実装に成功した。

研究グループは,ウェアラブルIoT機器のみならず,ドローン,自動車内エンタメ機器制御,AR/VR機器への応用が期待されるとしている。