東京工業大学の研究グループは,PLLのオーバーサンプリングを非均一に行う新しいアーキテクチャによる,低消費電力・低ジッタ特性のデジタル位相同期回路(PLL)の開発に成功した(ニュースリリース)。

東京工業大学の研究グループは,PLLのオーバーサンプリングを非均一に行う新しいアーキテクチャによる,低消費電力・低ジッタ特性のデジタル位相同期回路(PLL)の開発に成功した(ニュースリリース)。

32kHzの水晶振動子から直接高周波の基準信号を生成するデジタル位相同期回路(Phase-Locked Loop:PLL)は,高周波用の振動子を不要にできることから,無線機器用の集積回路の小型・低消費電力化,低コスト化に大きく貢献してきた。

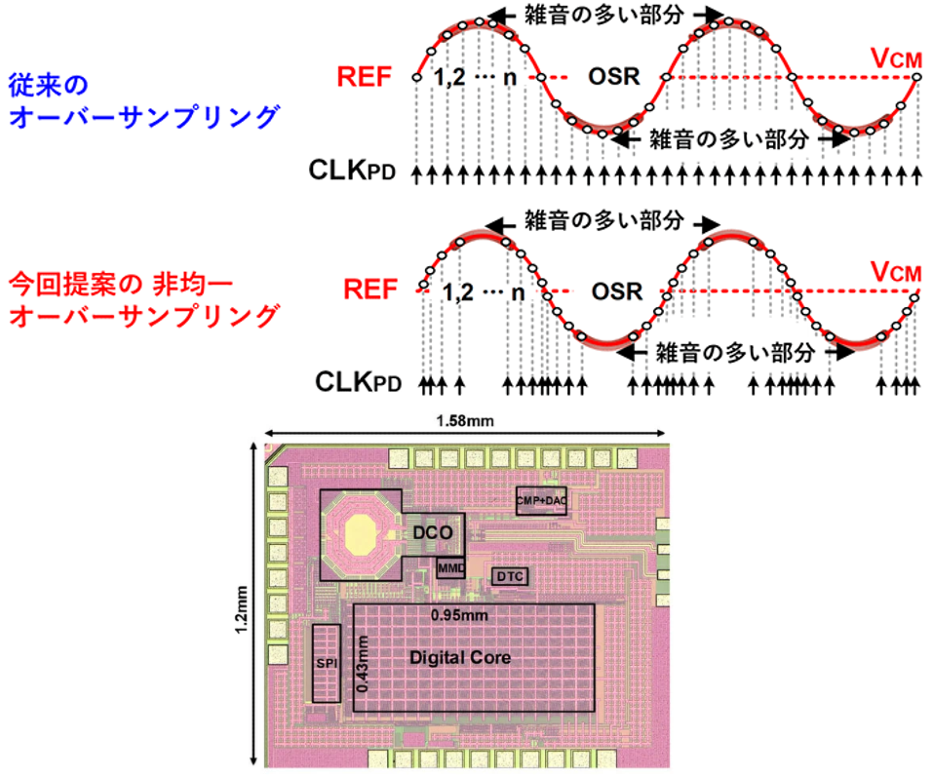

しかしながら,32kHzという低い参照信号によるPLLにはループ帯域幅が小さいという課題があった。この課題を解決するために,オーバーサンプリングの手法によってループ帯域幅を向上する提案がなされたが,従来の均一なオーバーサンプリングでは,参照電圧信号の雑音によってジッタが発生することが問題となっていた。

ジッタは,高周波デジタル信号を使用する最新の電子機器に共通する大きな問題であり,特にIoTに向けた無線機器には小型・低消費電力の低ジッタPLLが強く求められていた。

今回の研究で開発したPLLでは,従来のオーバーサンプリングの課題を解決するため,オーバーサンプリングの間隔を非均一にする新しいアーキテクチャを提案し,ジッタを大きく低減した。

今回提案した非均一なオーバーサンプリング手法では,参照電圧信号のうち,雑音の多い部分は従来よりもサンプリングを減らし,他の部分を密にサンプリングする。これにより,位相検出器からのノイズの影響を低減し,PLLのジッタを大きく削減できるという。

このアーキテクチャを用いたデジタルPLL回路を,65nmのCMOSプロセスを用いて実際に作製した。チップサイズは1.58mmx1.2mmで,新たに開発した利得増大位相検出器を内蔵し,異なるサンプリングポイントのループ利得を動的に調整できるようにした。

作製した回路を評価した結果,200kHzのループ帯域幅を4.95psの低ジッタで実現できていることがわかった。消費電力は3.8mWだった。

開発したPLLは,高いエネルギー効率を必要とするアプリケーションの実現に貢献する。開発したPLL,世代通信ネットワークの要となる低消費電力Beyond 5Gデバイスにも応用でき、IoTデバイスの普及を一気に加速することが期待できる。

さらに研究グループは,次世代センサーデバイス,パワーデバイス等の多くのアプリケーションが研究の恩恵を受けるとしている。