東京工業大学,北海道大学,日立北大ラボ(日立製作所と北海道大学が開設したオープンラボ),東京大学の研究グループは,組合せ最適化問題を高速に解くことができる新しいアニーリング処理方式と,それを利用した新しいプロセッサLSIの開発に成功した(ニュースリリース)。

東京工業大学,北海道大学,日立北大ラボ(日立製作所と北海道大学が開設したオープンラボ),東京大学の研究グループは,組合せ最適化問題を高速に解くことができる新しいアニーリング処理方式と,それを利用した新しいプロセッサLSIの開発に成功した(ニュースリリース)。

組合せ最適化問題の近似的な計算技法であるアニーリング処理には「局所型」と「全結合型」の2つがあり,後者の方が応用範囲は格段に広い反面,高速に解くのが難しい。このため,これまで全結合型のアニーリング処理を行なうプロセッサLSIは存在していなかった。

研究ではまず,組合せ最適化問題を高速に解くことができる新しいアニーリング処理モデル「ストカスティック(確率的)・セルラー・オートマタ」(SCA)を構築した。従来のアニーリングマシンは基本的には「シミュレーテッド・アニーリング」(SA)か,SAに類似する計算手法をベースにしていた。

SAでは原理的に,ある疑似スピンの値が変わると,これとつながる全ての疑似スピンに与える影響を改めて計算する必要があった。このため,疑似スピンの値の更新は逐次的にならざるを得なかった。これに対し,SCAでは全疑似スピンの値を並列に更新することができる。

研究グループは,このSCAによってSAと同じ最適解を探せることを数学的に証明し,SCAを用いたアニーリングプロセッサLSIが実現可能であることを明らかにした。

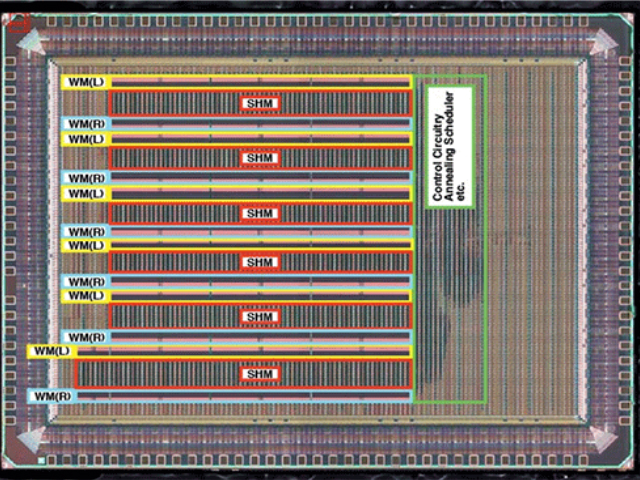

SCAにおける並列な疑似スピン更新は,更新したい疑似スピンにかかる相互作用係数を読み出し,現在の疑似スピンの値と演算することで行なわれる。この理解をもとに,相互作用係数をメモリに記憶させ,そのメモリから並列に相互作用係数を読み出し,メモリに付随したロジック回路で並列演算することでSCAの計算を効率よく実行できることを発見し,このニアメモリ型のアーキテクチャを「STATICA」と名付けた。

このアーキテクチャに基づいて,512疑似スピンの並列更新ができるように構成したアニーリングプロセッサLSI「STATICA」を開発した。台湾TSMCの65nmプロセスで試作したチップで,3mm×4mmの大きさで512疑似スピンからなるイジングモデルのアニーリング処理を並列に実行でき,消費電力は600mW程度。

STATICA技術は既存技術と比べて,アニーリング速度,消費電力,答えの精度のいずれにおいても,非常に高い指標を達成することができる(少なくともアニーリング速度では数倍,エネルギー効率では2桁以上の向上)という。

今後は,さらに複雑で大規模な組合せ最適化問題を高速に解くことを目指して,開発したチップのキャパシティ強化を進めていくとしている。