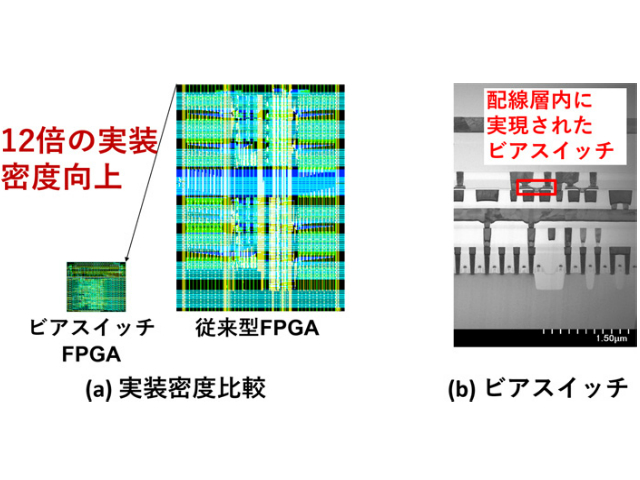

大阪大学の研究グループは,新ナノデバイスであるビアスイッチをFPGA(Field Programmable Gate Array)のプログラム機能実現に利用することで,FPGAチップの12倍の高密度化実装に世界で初めて成功した(ニュースリリース)。

大阪大学の研究グループは,新ナノデバイスであるビアスイッチをFPGA(Field Programmable Gate Array)のプログラム機能実現に利用することで,FPGAチップの12倍の高密度化実装に世界で初めて成功した(ニュースリリース)。

ビアスイッチとは,配線層内に実現された不揮発スイッチ(原子スイッチ)とプログラム用の選択デバイス(バリスタ)からなるデバイス。プログラムを制御するためのアクセストランジスタが不要のため,配線層内に小面積で実装できる特長を持つ。

これまでFPGAは,短期間で機能実現でき,少量多品種の製品に適するという特徴により利用拡大が進んできた。しかし,チップ内のプログラミング機能の実現に多数のトランジスタを利用するため,チップの実装密度が低く,動作速度や消費電力などの性能が低いという課題があった。

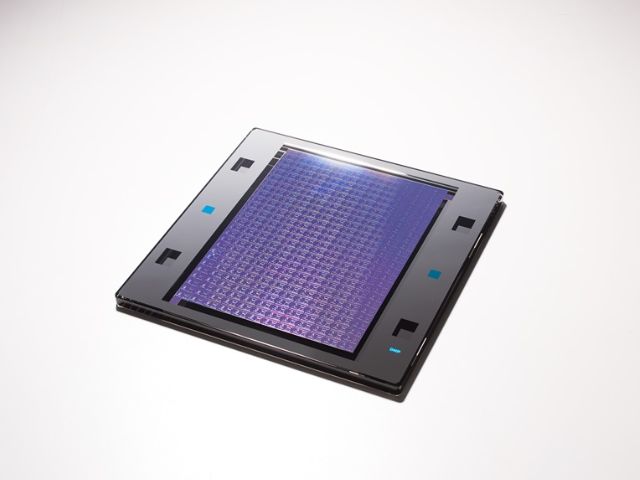

研究グループでは今回,ビアスイッチを用いたFPGAの試作に世界で初めて成功し,従来のトランジスタでプログラム機能を実現するFPGAに対して,12倍の実装密度向上を実証した。

実装密度はFPGAチップの価格に直結するため,大幅なコスト低減が期待できる。また,プログラム機能の実現にトランジスタを利用しなくなったため,全てのトランジスタをコンピューティングに利用できるようになり,高いコンピューティング性能の実現も可能となる。

最小線幅65nmのシリコンCMOSプロセスを用いて製造したFPGAチップをプログラミングし,期待通りの機能が実現できていることを確認した。ビアスイッチが次世代のFPGAに適したデバイスであることを明らかにした。

さらに,AIアプリケーションが効率的に実現できるFPGAアーキテクチャを開発し,その性能予測を行なった。トランジスタを用いてプログラミング機能を実現したFPGAに対して,5倍のエネルギー効率向上が可能であることもわかった。最小線幅7nmのシリコンCMOSプロセスで製造した場合,さらに11倍のエネルギー効率向上が期待できるという。

この研究成果により,AIアプリケーションを実現するプラットフォームとして期待が集まるFPGAデバイスの性能並びにエネルギー効率を向上させることができるという。さらに高密度化により,FPGAデバイスの低価格化も期待できるとしている。