三菱電機と東京大学は,世界で初めて,パワー半導体モジュールに搭載されるSiCパワー半導体素子の抵抗の大きさを左右する電子散乱を起こす3つの要因の影響度を解明するとともに,要因の一つである電荷による電子散乱の抑制により,界面下の抵抗が従来比3分の1に低減することを確認した(ニュースリリース)。

三菱電機と東京大学は,世界で初めて,パワー半導体モジュールに搭載されるSiCパワー半導体素子の抵抗の大きさを左右する電子散乱を起こす3つの要因の影響度を解明するとともに,要因の一つである電荷による電子散乱の抑制により,界面下の抵抗が従来比3分の1に低減することを確認した(ニュースリリース)。

パワーエレクトロニクス機器のキーパーツであるパワー半導体モジュールの素子に,従来のSiパワー半導体素子に比べ抵抗が少ないSiCパワー半導体素子を採用し,電力損失の低減を実現する動きが加速している。

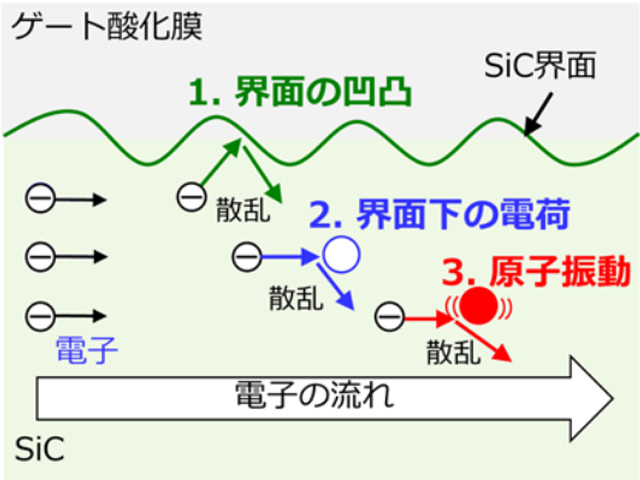

SiCパワー半導体素子の低抵抗化をさらに進めるためには,界面下の抵抗特性を正しく理解することが必要だが,これまでは抵抗の大きさを左右する電子散乱を起こす,界面の凹凸・界面下の電荷・原子振動の3つの要因の影響度を分離して測定することが困難だった。

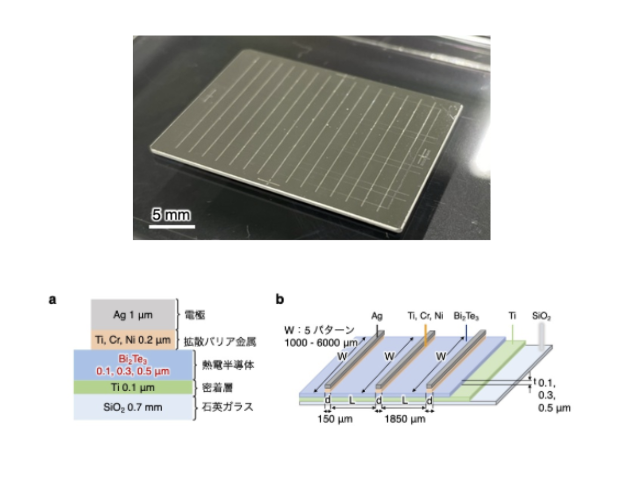

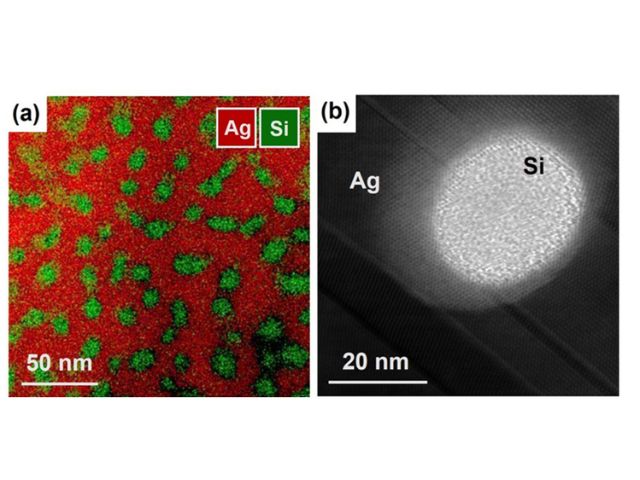

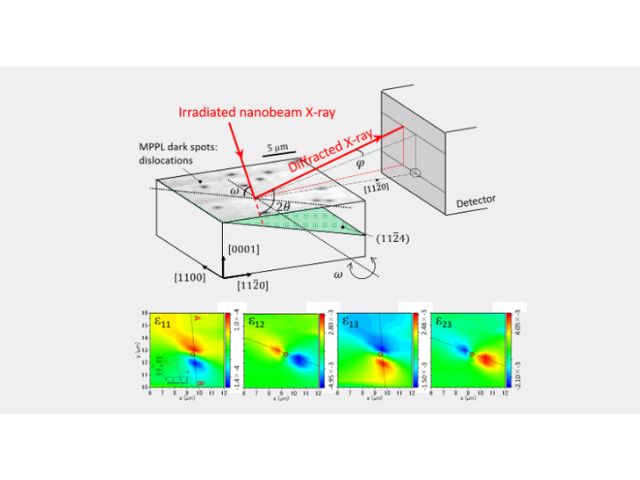

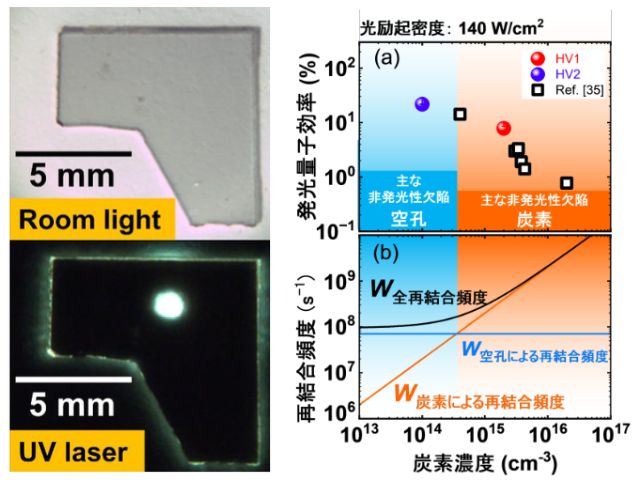

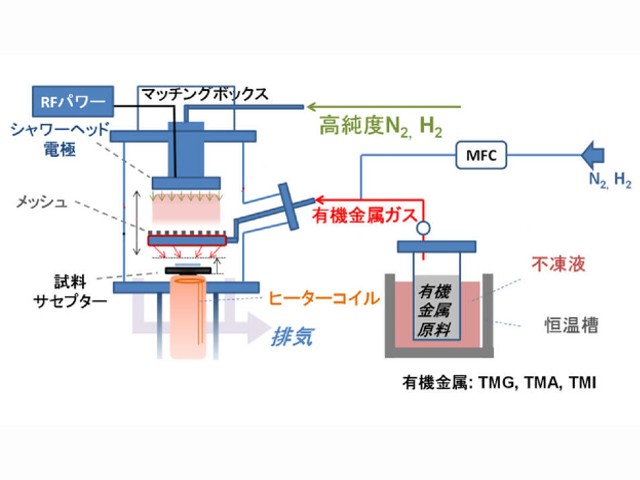

今回,界面下の電荷による影響を確認するため,電子が流れる領域を界面から数十ナノメートル遠ざけた横型の抵抗評価用素子(SiC-MOSFET)を作製した。原子振動に着目し,SiC界面近くの電子散乱を東京大学の評価技術で測定したところ,SiCの抵抗を左右する電子散乱を起こす3つの要因のうち,界面の凹凸の影響は小さく,界面下の電荷と原子振動の影響が大きいことを実験により世界で初めて解明した。

また,横型の抵抗評価用素子において,界面下の電荷から電子の流れを遠ざけることで電荷による電子散乱を抑制し,界面下の抵抗を従来比3分の1に低減することを確認した。

今後,この成果をもとにSiC-MOSFETの設計と試作評価を実施し,より一層抵抗の少ないSiCパワー半導体素子の実現にむけた研究開発を推進するとしている。