2. シミュレーションによる液晶素子の設計

透明電極に,絶縁層を隔てて形成された高抵抗層は,空間的な電位分布を緩やかにする働きがあることが知られており,これを用いることで,従来は数十Vrmsが必要だった液晶レンズの駆動電圧を,3.5 Vrmsに低減できたという実績がある1, 4, 7)。

一方,高抵抗層を用いない従来の構造では,空間の電位分布は電極のエッジ部分で急激に変化する。我々は,これらの異なる分布の性質を利用できないかと考え,検討を進めた12)。設計と評価には,有限要素法による電磁界解析ソフト(COMSOL社,COMSOL Multiphysics)を用いた。

簡単のため,シミュレーションモデルは2次元とし,無限に長い平行な電極と,絶縁層および高抵抗層を用いて,液晶層内にブレーズ状の電位分布を形成できる素子構造の創出を試みた。

3. サンプルの作製

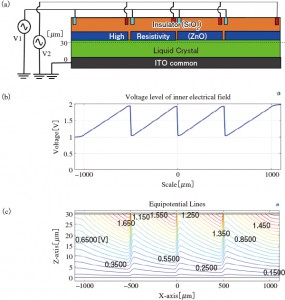

図2(a)に,今回設計したフレネル型構造を持つ液晶偏向素子の断面の概略図を示す。図示しない2つの透明ガラス基板に上下を挟まれた,2種類の異なる電圧を印加できる各4本の細長い電極(インジウム錫酸化物,ITO)が,大小2種の間隔を隔てて交互に配置されており,その間は絶縁層(SiO2)によって隔絶されている。

絶縁層の層厚は500 nmに設定し,電極の層厚は25 nmと,絶縁層よりも十分に薄い値に設定した。絶縁層の下方には,層厚250 nmの高抵抗層(主成分ZnO)が設けられており,高抵抗層には,上方の電極の間隔の狭い部分に一致して,絶縁層による同間隔のギャップを設けている。絶縁層の下方には,層厚30μmの液晶層が設けられており,その下方には,共通電極が前記の電極と同じ層厚で配置されている。

このような配置にして,高抵抗層の比抵抗を1×103Ωmに設定し,印加電圧(V1,V2)をそれぞれ(2.0,1.0)Vrmsとし,その周波数を100 Hzとして,前述の電極の交互に,V1とV2の異なる2種の交流電圧を印加した状態を想定して,共通電極から30μmの位置における液晶層内の電位分布を算出した。その結果を図2(b)に示す。

このように,電極の間隔の広い領域では電位が緩やかに変化し,同間隔の狭い領域では電位が急峻に変化することで,ブレーズ状の電位分布を液晶層内に得ることができた。前者の緩やかな変化は下方に設けた高抵抗層の影響であり,後者の急峻な変化は高抵抗層に設けた絶縁層のギャップによる影響である。

また,この時の液晶層内に発生する電界の等電位面を算出した結果を図2(c)に示す。絶縁層と高抵抗層の影響で,ブレーズ型の電位分布が液晶層内に形成されていることが確認できた。