東京工業大学の研究グループは,バンプレスChip-on-Wafer(COW)プロセスおよびWafer-on-Wafer(WOW)プロセスによって,CPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を創出した(ニュースリリース)。

東京工業大学の研究グループは,バンプレスChip-on-Wafer(COW)プロセスおよびWafer-on-Wafer(WOW)プロセスによって,CPU/GPUとメモリを3次元実装するハイブリッド3次元実装技術「BBCube 3D」を創出した(ニュースリリース)。

AIやHPC(High Performance Computing)では,CPU/GPUとメモリとの間で大量のデータ伝送することが要求される。これに応えるためにデータ伝送のスピードを1秒間に100億ビットまで増加させ,Siインターポーザで多くのデータを送受する場合,4千~6千本までの配線を必要としていた。

しかし,従来の2次元的な配置では配線数をこれ以上増やすことは物理的に難しい。また,伝送距離とデータ伝送速度に比例した消費電力の増大が課題となっている。

また,従来の3次元積層による半導体パッケージでは,チップの垂直配線同士の接続にマイクロバンプを用いており,垂直配線の高密度化やデータ伝送消費電力増大の一因となる寄生容量の低減が困難という問題があった。

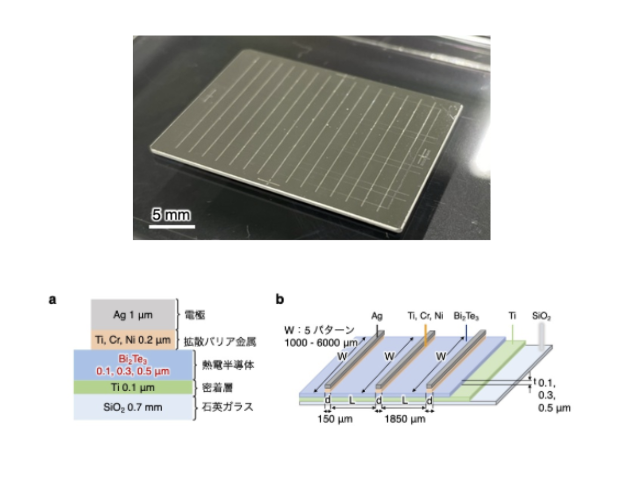

研究グループは,銅を配線に用い,埋め込み・研磨によって垂直配線を行うバンプレスプロセスを用いて,CPU/GPUとメモリとを3次元積層するBBCube 3Dを提案することで,AI HPC向け半導体のCPU/GPUとメモリ間データ伝送の高帯域と消費電力低減の両立を目指した。

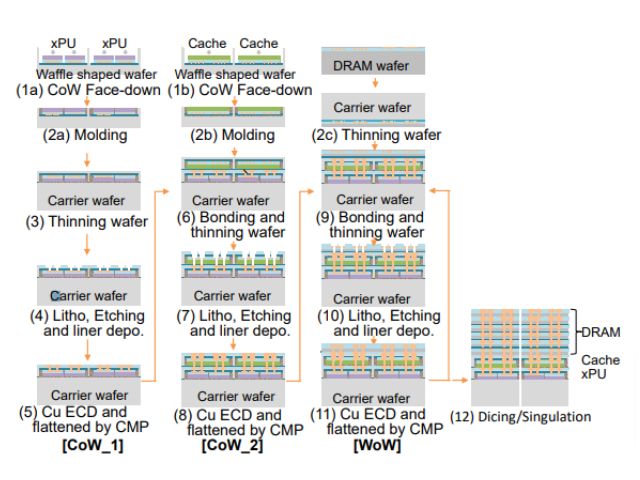

まず,ワッフル状にしたウエハーであるワッフルウエハーにCPUまたはGPUのチップを搭載し,モールディングして,ウエハーを薄化,TSVを形成する。同様にキャッシュチップをワッフルウエハーに搭載し,モールディングして,CPU/GPUのウエハーに積層し薄化する。

その後TSVを形成してCPU/GPUとキャッシュとを接続する。DRAMはDRAMウエハーをキャリアウエハーに貼付け,薄化する。

さらに,CPU/GPU,キャッシュを搭載したウエハーに積層し,TSVを形成して,キャッシュとDRAMを接続する。これらを繰り返して,DRAMを必要層数積層した後,ダイシングして個別のチップに分ける。

比較の結果,BBCube 3DはDDR5の13倍,HBM2E(高帯域メモリ)の4倍の高帯域なデータ伝送を実現しながら,電力はそれぞれに対し1/20,1/5に抑えることが可能となった。

今回開発したBBCube 3Dにより,AI,HPC用半導体の電力を大幅に低減することが可能となる。研究グループは,CPU/GPUとメモリをバンプレスWOW,COWで積層したBBCube 3Dを試作し,大容量データ伝送と低消費電力の両立の実証を目指すとしている。