KDDI総合研究所と早稲田大学は,AIの低消費電力化と高速化の実現を目指し,従来比で約17分の1の面積の光AIアクセラレーター用シリコン光回路を試作し,時系列データの予測を行なうことに成功した(ニュースリリース)。

KDDI総合研究所と早稲田大学は,AIの低消費電力化と高速化の実現を目指し,従来比で約17分の1の面積の光AIアクセラレーター用シリコン光回路を試作し,時系列データの予測を行なうことに成功した(ニュースリリース)。

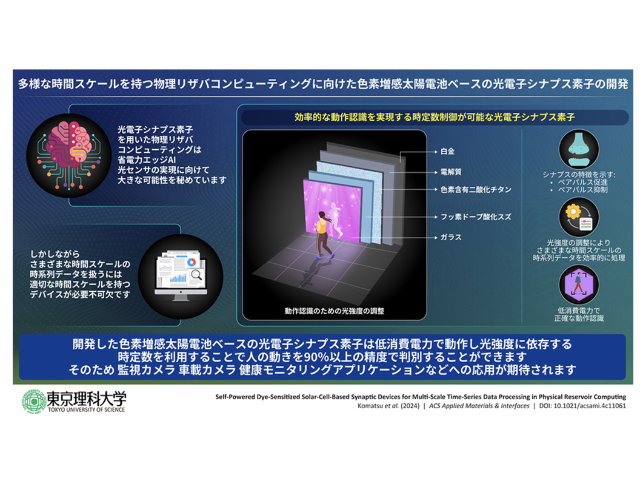

最先端を走るAIでは,消費電力の削減や処理の高速化が課題となっている。一般に用いられるAIは電子回路上で動作しているが,一部の演算を光回路に置き換える光AIアクセラレーターは,消費電力の削減に有効で,かつ学習や推論の高速化が可能なことから,研究開発が盛んになっている。

中でもシリコン上に形成した光回路は,電子回路や他の光素子との集積化が容易な上,小型化できると期待されている。一方で光アクセラレーターを実用化するには,大規模に集積しやすくする必要があり,より一層の小型化が求められている。

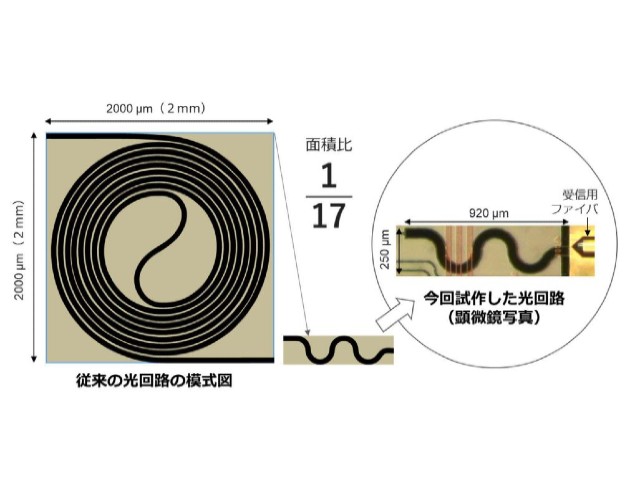

研究グループは,従来比で約17分の1の面積の光AIアクセラレーター用シリコン光回路を試作し,時系列データの予測を行なった。

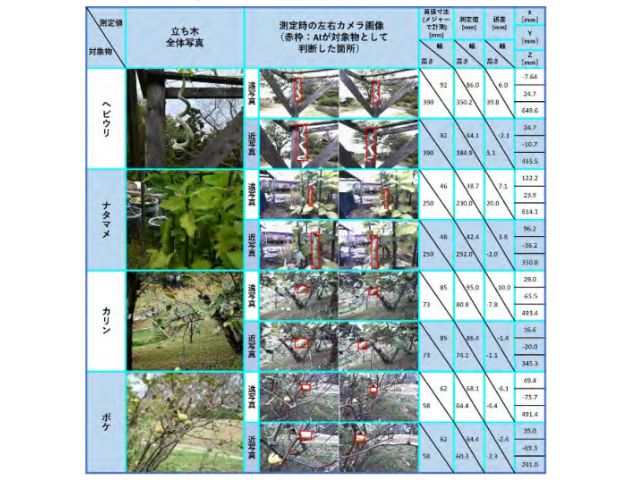

シリコン上に光回路(面積:0.25mm×0.92mm)を試作し,性能比較のため標準的に用いられているタスクであるSanta Fe波形の予測をさせたところ,正解データと予測データの誤差が非常に小さく,その構造の有効性を示すことができた。

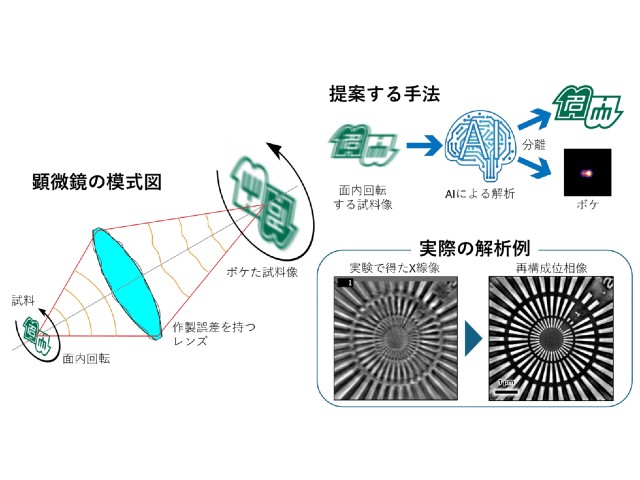

これまで研究されてきたシリコン上に形成した光回路では,AIのモデルの一つであるリザバーコンピューティングを動作させるために,現在の情報と過去の情報を混ぜ合わせる必要があり,以下のいずれかの構造を採用していた。

①信号をネットワーク状に形成された光回路で何度も混ぜ合わせる構造:現在の情報と過去の情報が効果的に混ざるようなタイミングとするためにネットワークの節間の距離を確保する必要があり,素子面積が広くなる(16mm2)。ニューロン数(神経細胞数)を増やすとさらなる面積が必要。

②長い渦巻き状マルチモード光導波路構造:進む速度が異なる光波が多数存在できるマルチモード光導波路の性質を利用して現在の情報と過去の情報とを混ぜ合わせるために長い(4cm程度)光導波路が必要とされる。渦巻き状に収容しても2mm×2mm程度の面積が必要。

今回の試作では,構造②に比べて導波路幅を2倍広くし,さらには蛇行状の導波路構造を採用して長さを調整することにより,短い導波路長でゆっくりと進む光波(高次モード)を多数発生させ,さらには信号の高速化することで現在の情報と過去の情報が十分に混ざり合うように設計した。

研究グループは今後,GPUベースのAIアクセラレーターに比べて10分の1の低消費電力,かつ高速な光AIチップの基盤技術の確立を目指すとしている。