産業技術総合研究所と日本電信電話は,電子回路ではなく,シリコン光集積回路を使った超低遅延かつ消費電力の少ないニューラルネットワーク演算技術を開発した(ニュースリリース)。

産業技術総合研究所と日本電信電話は,電子回路ではなく,シリコン光集積回路を使った超低遅延かつ消費電力の少ないニューラルネットワーク演算技術を開発した(ニュースリリース)。

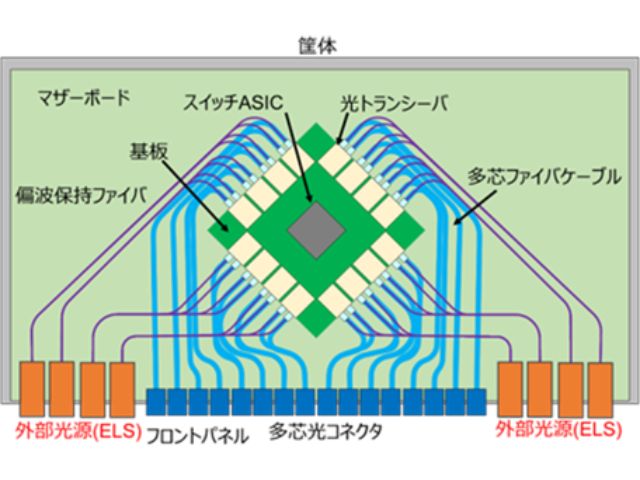

現在の光ニューラルネットワーク演算回路は,光信号を電気信号に変換し,電子回路によるデジタル演算でこれを実現するハイブリッドな構成となっている。そのため,消費電力と演算遅延において,そのメリットが活かされていなかった。

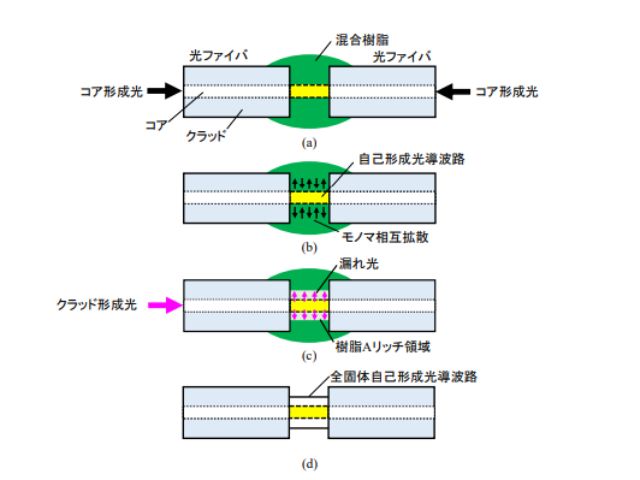

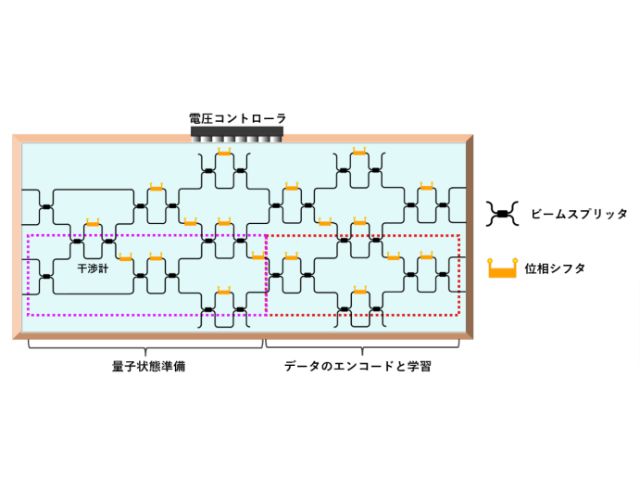

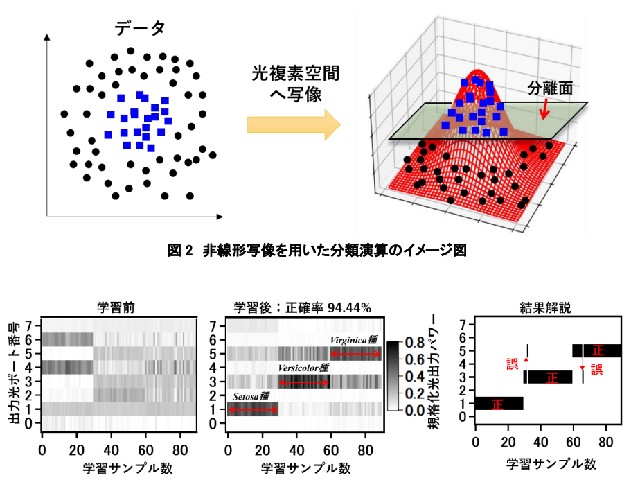

研究では,光干渉計デバイスの駆動電圧に対する非線形性を用いるために,非線形写像型のニューラルネット演算方式を提案した。この演算方式では,データ入力部の光干渉計デバイスにより,解析すべきデータを高次元光複素振幅空間に非線形写像し,さらに多数の光干渉計から構成される光集積回路に光伝搬させることにより演算結果を得る。

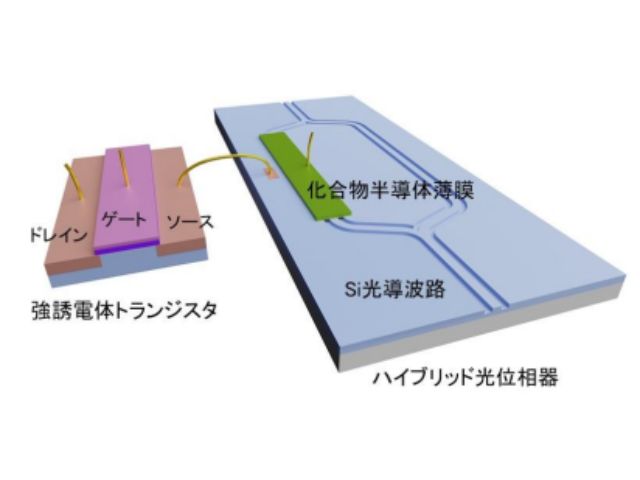

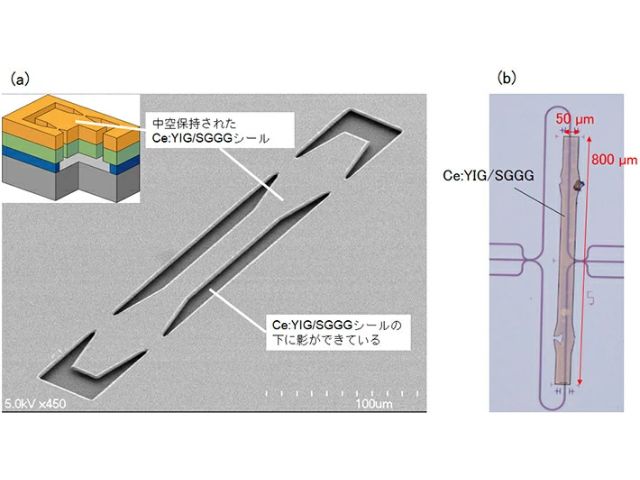

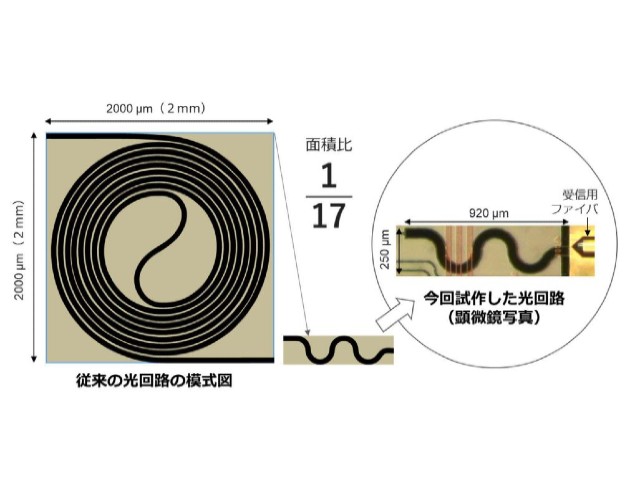

この演算方式を検証するための光集積回路をシリコンフォトニクス技術により製作した。この回路は,シリコン導波路型マッハツェンダー光干渉計(MZI)および単体位相シフタを基本要素としたメッシュ構造となっている。MZIや単体位相シフタは導波路近傍に配置されたヒーターによる熱光学効果で動作する。

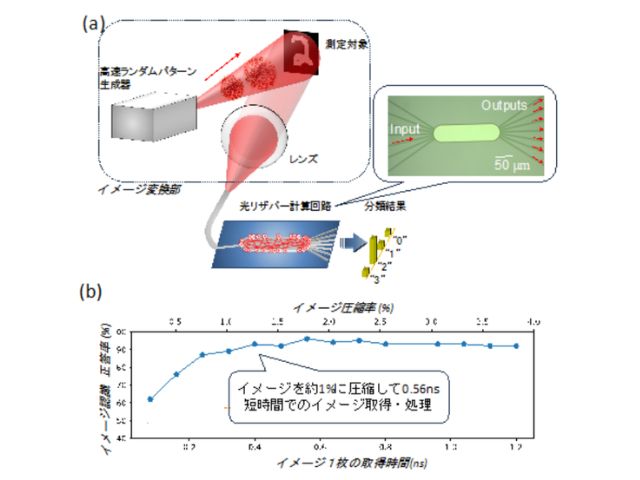

解析すべきデータは電気信号としてMZIに入力され,光信号に変換される。その際に,MZIの非線形応答により,入力データが高次元複素振幅空間に写像される。入力部を通過した光信号は,その後に控えている積和演算部を通過し,そこでの演算を経て,分類の境界を与える高次元平面が算出される。最終的な分類演算結果は,最大光パワーを示す出力ポートの位置で示される。

デバイスにある干渉計パラメーターの設定は,機械学習により実施された。学習には細菌採餌最適化アルゴリズム(BFO),あるいは前方伝搬アルゴリズム(FP)を利用し,回路実機に対し直接に学習を実施した。回路実機による直接学習は,外部コンピューターによる事前学習とは異なり,自らの経験に基づいた自律的な学習習熟度の向上を可能とする。

アヤメの花弁サイズからアヤメの種類を判別する分類演算用ベンチマークテストでは,90サンプルの学習後,約94%の正答率で分類が可能となった。さらに,学習に用いていない60サンプルに対しても分類を行ない,約97%の正答率も得た。

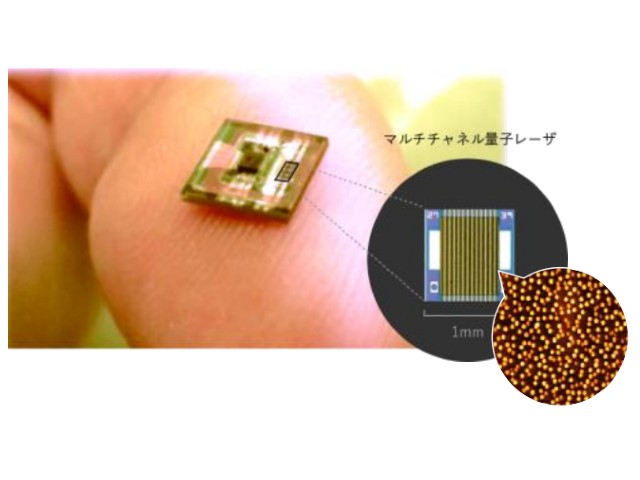

分類演算の処理時間は100ピコ秒以下と,デジタル電子回路演算の約千分の一で,回路パラメーターの設定に要したヒーター電力は約360ミリワットと,デジタル電子回路演算の数十分の一だった。さらに,ヒーター方式からPN接合型高速シリコン光変調器に変更することにより,原理的には毎秒数100億回の高スループット演算も可能だという。

研究グループは,今回提案した非線形写像型の演算方式をベースに,幅広くかつ実用性の高い応用への適合性の確認を進めるとしている。