東京理科大学の研究グループは,現在のコンピュータより遥かに高速,省エネルギーな計算力に期待のかかる「量子コンピュータ」について,計算に使用する量子ビットの新たな回路方式を提示した(ニュースリリース)。

東京理科大学の研究グループは,現在のコンピュータより遥かに高速,省エネルギーな計算力に期待のかかる「量子コンピュータ」について,計算に使用する量子ビットの新たな回路方式を提示した(ニュースリリース)。

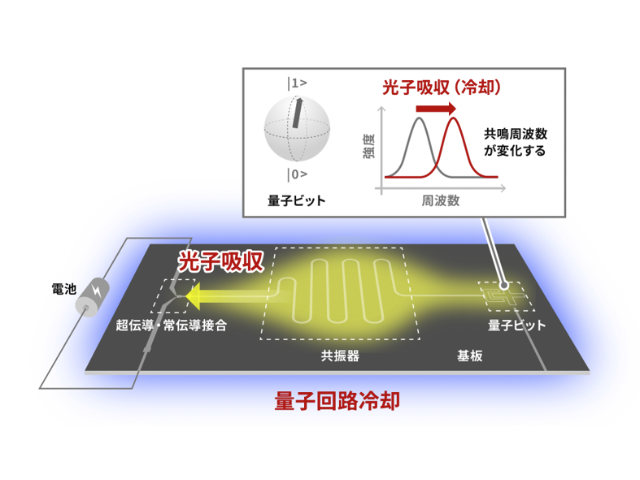

量子ビットが持つ量子の状態は,観測の影響だけでなく,周囲の環境などの影響によっても影響をうける為,量子ビットは古典的なビットと比べてエラーが起こりやすく,また多数の量子ビットを同時に稼働させることも容易ではない。

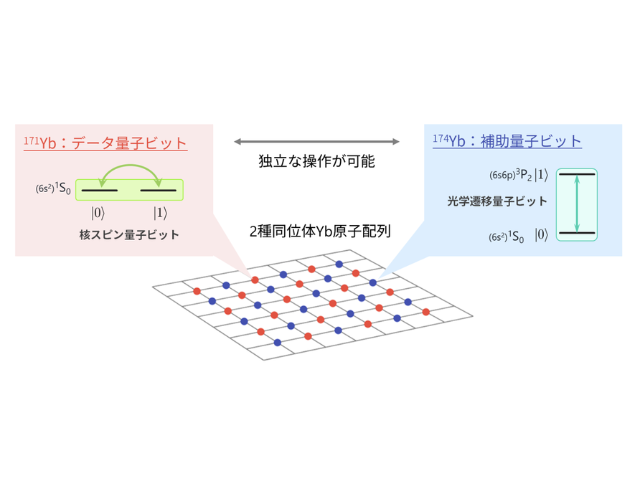

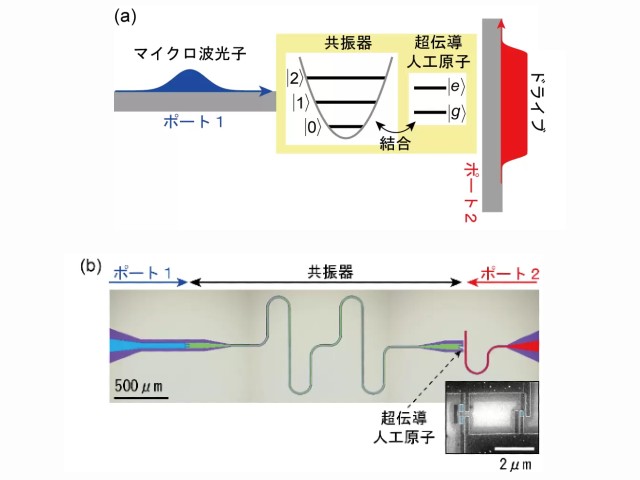

現存する多くの理論提案では,量子コンピュータは,量子ビットが2次元(平面)格子状に配置され,その他の配線や機器に接続されている。配置された量子ビットが増えると,2次元格子の中心付近に配置された量子ビットには操作や状態の測定のための配線を伸ばすことが難しくなってくる。

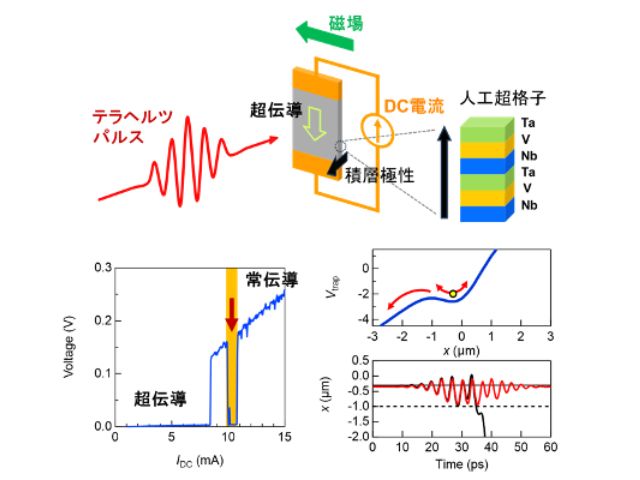

そこで,主流な集積化の研究では3次元(垂直)配線による量子ビットへの個別配線が研究されている。しかし,3次元配線は未だ新しい技術であり,技術的困難がある。

研究グループは今回の研究について,3次元の配線技術を必要とせず,完全に平面的な配置を維持できるような,超伝導量子ビットの集積回路方式を提示することで,この問題を解決したいと考えたという。

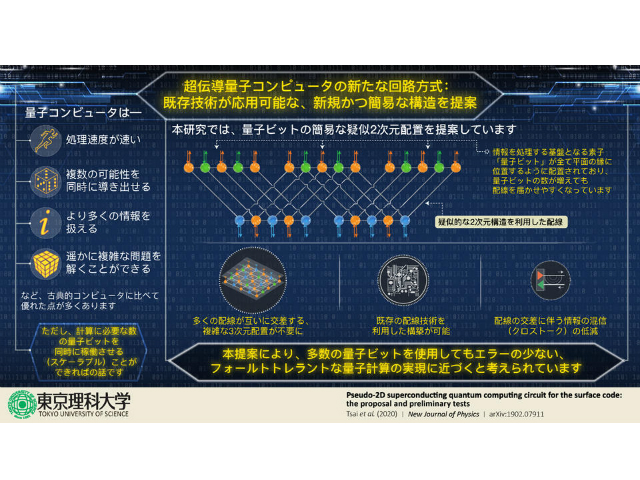

まずは量子ビットを「2次元に配置したまま」,全ての量子ビットへの配線も平面に配置する新しい回路方法を提示した。これは,量子ビットの正方格子を,それぞれの並びごとに,巧妙に折り畳むことで「量子ビットが2列に並んだ(bi-linear array)」新たな配置ができあがる。

この形状を取ることにより,2次元配置を崩さないまま,全ての量子ビットを縁に出して簡易な平面配線を実現できる。これによって配線間の混信や,損失が低減され,複数の量子ビットのエラーが抑えられ,それらで構成される論理量子ビットの信頼性の向上に繋がると期待されている。

2列に並んだ形であっても,元の隣り合う量子ビットのつながり方は維持する必要があり,そのために一部の量子ビットをつなぐ配線に交差が生じる。これは局所的な立体構造を使用することで実現できる。

研究グループは,このような立体構造の寄与を調べ,評価した。その結果,現状の技術を用いても十分に実現可能な回路であることが示された。3次元配列を一切使わなくても,既存の2次元配列技術を応用して,量子コンピュータの実装が平面回路で実現可能であるということを示唆している。

今回提示された回路方式は,情報の損失やエラーを減らし,より信頼性のある量子ビットを集積することを可能にし,スケーラブルな量子コンピュータの実現に貢献するとしている。