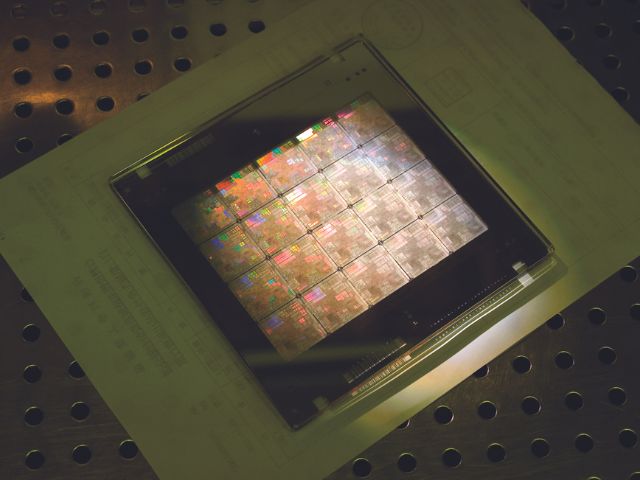

東京理科大学の研究グループは,組み合わせ最適化問題の求解用に世界で初めて全結合型半導体アニーリング方式を搭載した人工知能集積回路(AIチップ)を開発し,LSIに実装した(ニュースリリース)。

東京理科大学の研究グループは,組み合わせ最適化問題の求解用に世界で初めて全結合型半導体アニーリング方式を搭載した人工知能集積回路(AIチップ)を開発し,LSIに実装した(ニュースリリース)。

組み合わせ最適化問題に対して,複数の計算要素(スピン。スピン一つにつき,上向きか下向きの二つの状態のいずれかを持つ)と,スピンの間の結合の強さ(相互作用)を調整し,スピンの向きを計算するための磁性体モデル(イジングモデル)の原理を応用した「アニーリング方式」によるAIチップの開発と,半導体集積回路(LSIチップ)化が進められている。

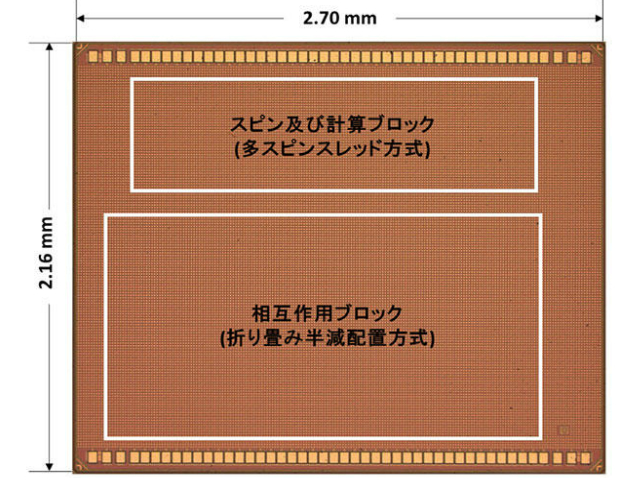

今回研究グループは,スピン同士のすべてを結合させる全結合方式のAIチップを開発し,世界で初めてLSIに実装した。搭載したスピン数は512個であり,22都市の巡回セールスマン問題を1秒以下で解くことが可能だとする。

全結合方式には,少ないスピン数で幅広い問題が解けるという利点があることが,LSIチップ化のためには,配線層数の制限から,すべてのスピンの結合を実装できる方法の開発が難しい課題だった。

今回,新しいチップアーキテクチャにより512個の全結合型スピンを搭載することが可能となった(チップ面積は28nm CMOS半導体プロセスで2.16mm×2.70mm)。

従来の隣接結合方式で今回の全結合型512スピンを実現しようとすると,およそ26万個のスピンが必要であり,更にこの26万個のスピン各々に対して,隣接結合ながら4~8個の結合回路が必要となる。実装面積が増大し,かつオーバーヘッド時間もこれに比例して大きくなってしまう。

また,今回搭載したスピン数512個では22都市の巡回セールスマン問題を解くことが可能だが,隣接結合LSIチップにおける既発表ではおよそ3万個のスピンを搭載したとされ,チップを2個使ったとしても16都市に相当した問題を解くのが限度だった。

22都市の場合と16都市の場合のそれぞれの解を30GOPSの従来型高性能CPUを想定して総当たり的に探索すると,前者ではおよそ1200年,後者ではおよそ12分が必要となるという。

今回の技術を応用することで,小型・低電力ながら高性能なシステムを実現することができるため,オフィスや個人のタブレット型端末などの身近な環境で,多くの組み合わせの中から最適な解を容易に求められるようになるなど,幅広い応用が期待されるとしている。