東京工業大学の研究グループは,マイクロプロセッサやシステムオンチップ(SoC)のコアにおける待機時電力を削減するために用いられているパワーゲーティングに不揮発記憶を導入することで,そのエネルギー削減効率を従来技術に比べて飛躍的に向上できる技術を開発した(ニュースリリース)。

東京工業大学の研究グループは,マイクロプロセッサやシステムオンチップ(SoC)のコアにおける待機時電力を削減するために用いられているパワーゲーティングに不揮発記憶を導入することで,そのエネルギー削減効率を従来技術に比べて飛躍的に向上できる技術を開発した(ニュースリリース)。

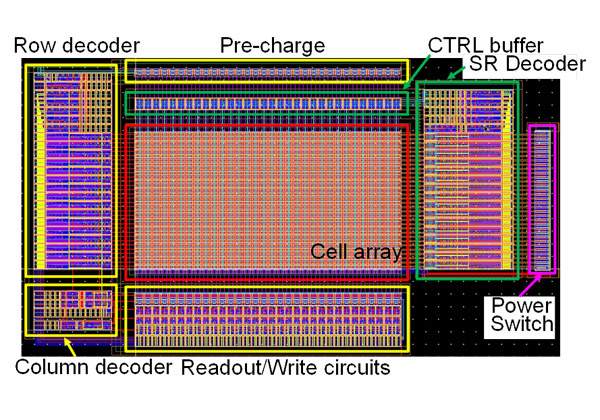

同グループが提案した不揮発性パワーゲーティング(NVPG)は,電源を遮断しても記憶内容を保持できる不揮発記憶を利用して,ロジックシステムの電源遮断を頻繁に行ない高効率に待機時電力を削減する方法。マイクロプロセッサやSoC内のコアに含まれるレジスタやキャッシュなどの記憶回路を独自開発の不揮発性双安定回路で構成して,通常動作をほとんど劣化させることなく,高効率にNVPGによるエネルギーの削減ができる。

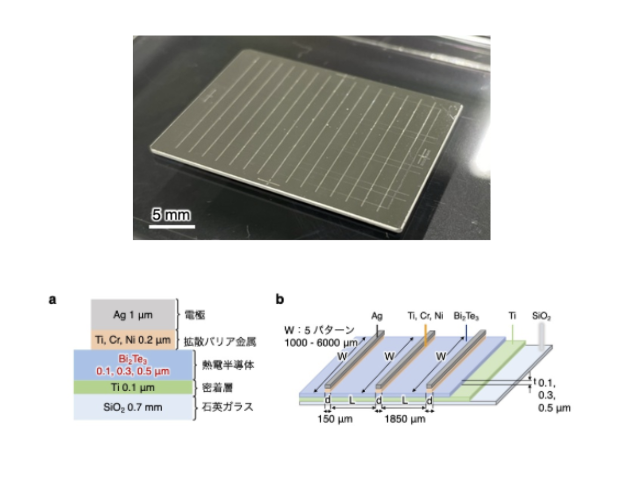

今回,同グループが提案している不揮発性SRAM(NV-SRAM)の設計法・駆動法を開発し,チップ試作を行ない,その実測結果の系統的な解析によって,NVPGがマイクロプロセッサやSoCにおけるコアの待機時電力の削減に極めて有効であることを明らかにした。

これまでにも不揮発記憶を用いたマイクロプロセッサやSoCのパワーゲーティングに関する技術開発はあったが,コア外の低階層キャッシュなどへの適応に限られていた。

今回の研究は,開発したNVPG技術がコアに含まれる高階層キャッシュに搭載することが可能で,コアレベルのパワーゲーティングによる待機時電力削減効率を飛躍的に向上できることを明らかにしたものだとしている。