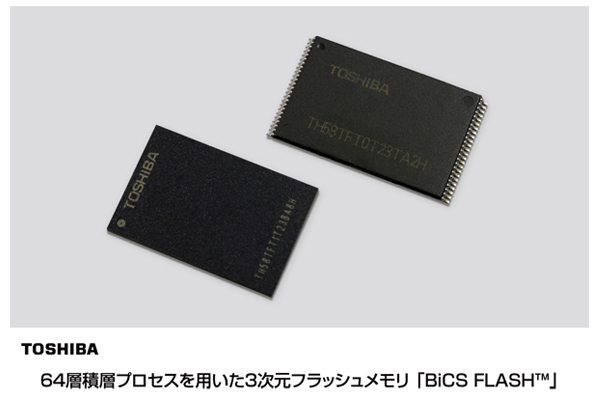

東芝は,3次元フラッシュメモリ「BiCS FLASHTM」の64層積層プロセスを開発し,7月27日から世界で初めてサンプル出荷を順次開始すると発表した(ニュースリリース)。

東芝は,3次元フラッシュメモリ「BiCS FLASHTM」の64層積層プロセスを開発し,7月27日から世界で初めてサンプル出荷を順次開始すると発表した(ニュースリリース)。

この製品は,256ギガビット(32ギガバイト)の3ビット/セル(TLC)。回路技術やプロセスを最適化することでチップサイズを小型化し,48層積層プロセスを用いたBiCS FLASHTMと比べて単位面積あたりのメモリ容量を約1.4倍に大容量化した。

また,チップサイズの小型化により1枚のシリコンウエハから生産されるメモリ容量を増やし,ビットあたりのコスト削減を実現した。

データセンター向けエンタープライズSSDやPC向けSSD,スマートフォン,タブレット,メモリカードなどを中心に市場のニーズに合わせて展開していく。

同社では,この製品を2016年7月に竣工した同社四日市工場の新・第2製造棟で,2017年前半より製造する予定。今後,64層積層プロセスを用いた512ギガビット(64ギガバイト)のBiCS FLASHTMの製品化も計画しているという。

2007年に3次元積層構造を用いたフラッシュメモリを世界で初めて公表した同社は,今後も継続して求められるメモリの大容量化,小型化など多様な市場のニーズに応えるためフラッシュメモリの3次元積層構造化を進めていくとしている。