東レは,光通信技術(シリコンフォトニクス)に用いられる光半導体(InP(インジウムリン)等)をシリコン基板上に実装するための材料および技術を開発した(ニュースリリース)。

AIの進展による高速通信の拡大により,電気通信よりも低エネルギー損失である光通信を,現在の長距離通信だけでなく,データセンター内で用いられる短距離(<1m)通信に適用するための開発が加速している。

この実現には,シリコン基板上に光回路を形成するシリコンフォトニクスが利用されるが,InP系等のⅢ-Ⅴ族化合物半導体をベースとした光半導体をシリコン基板上実装する必要がある。そして,大量で高速に実装する必要があり,そのためのマストランスファー技術が求められている。

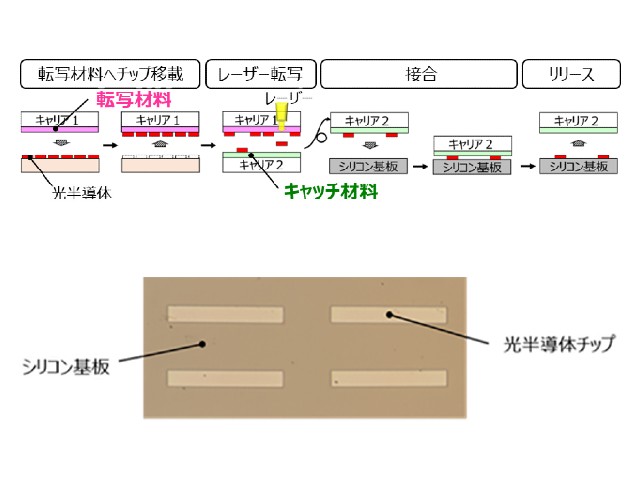

今回同社は,InP等の光半導体をレーザーで高速転写するための転写材料,および転写されたチップをキャッチしてそのままシリコン基板上に直接接合が可能なキャッチ材料,およびその実装プロセス技術について,東レエンジニアリング(TRENG)と連携して開発した。

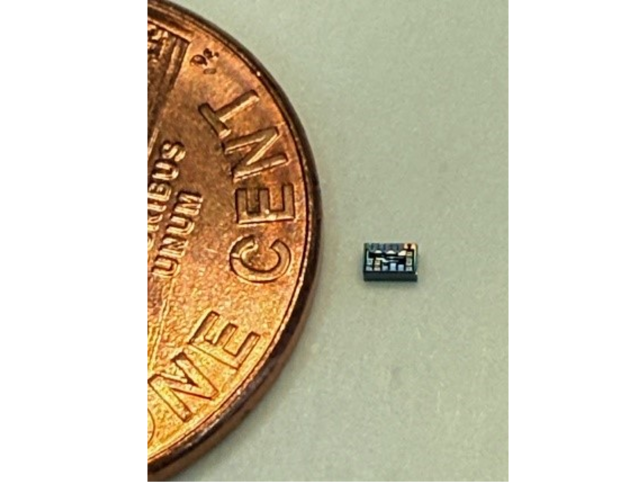

転写材料(耐衝撃性制御)について同社はマイクロLED向けの材料を開発済み。しかし,今回のInPベースの光半導体は縦横640μm×90μm,厚さ3μm以下と,一般的なマイクロLEDよりも縦横サイズは大きい一方,厚さが極端に薄い。今回,これを破損させることなく,一回のレーザー照射で転写可能な新規転写材料を開発した。

また,高速で飛翔してくるチップをキャッチするだけはなく、その後のチップのシリコン基板への直接接合(薬品で洗浄後,プラズマで接合面を活性化して≧200℃で加圧)に耐え,その後,容易にリリースできることを可能にするキャッチ材も新規に開発した。

これらの材料を用いて,レーザー転写からシリコン基板上への直接接合までの一連のプロセスをTRENGと連携して開発・実証した。現時点における接合後の位置精度は±2μm以内,回転ずれは±1°以内のレベルを確認しているという。

TRENGは,半導体実装用のボンダーおよびレーザーマストランスファーの設備技術を保有している。今回,光半導体の実装速度が大幅に向上し,6000個/分(従来のフリップチップボンダーでは約4個/分※同社調べ)の高速実装が可能となり,データセンター内での光通信適用の加速が見込まれるとする。

両者は今後も連携し,実デバイスを用いた技術確立を2025年までに実現し,早期の量産適用を目指すとしている。