信越化学は,半導体パッケージ基板製造装置と新工法を開発した(ニュースリリース)。

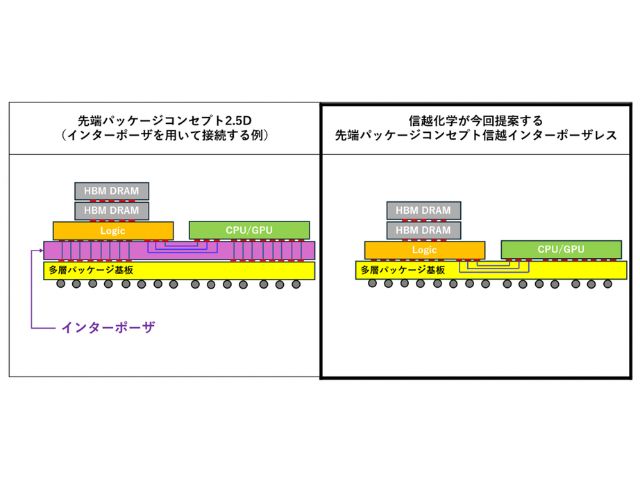

半導体の高性能化をコスト低減の面から支える技術として,回路を個片化して一つのパッケージに収めるチップレットが注目を集めている。この技術では,複数のチップレットを中間基板に搭載し,チップレット同士を接続する工程が必要とされており,この中間基板をインターポーザという。

新工法はインターポーザを不要とし,この工程を大幅に簡略化する。インターポーザと同様の機能を有した配線パターンを直接パッケージ基板に加工・形成することにより,チップレット間の接続をパッケージ基板上で行なう。チップレットを用いる先端半導体の更なる工程短縮,大幅なコストダウンが実現可能だという。

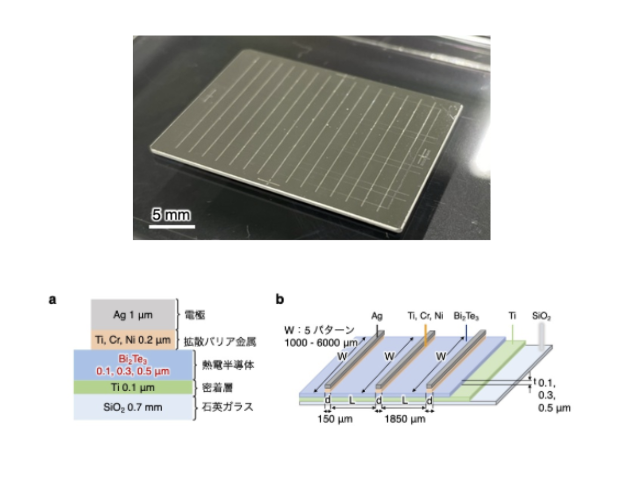

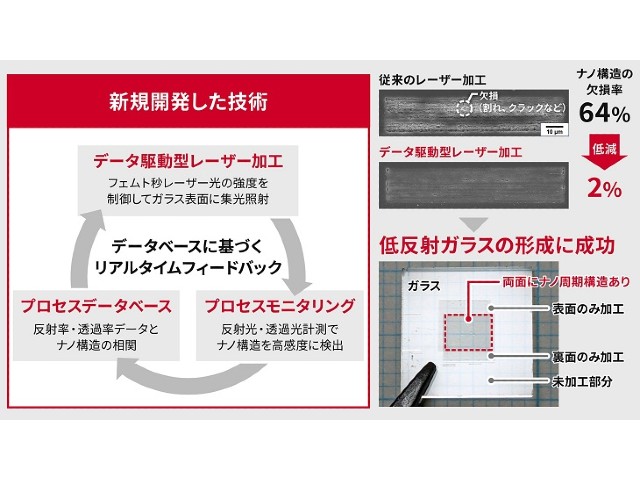

この装置の高度な微細加工の技術により,直接,多層パッケージ基板の各層に複雑な電気回路パターンを有機絶縁層の中に掘り込み,銅メッキで回路を形成することが可能となる。また,エキシマレーザーを光源として利用し,大面積の電気回路パターンを一括成形することができるという。

新工法を用いると,現在主流のドライフィルムレジストを使用するセミアディティブプロセス(SAP)法では達成できなかった微細加工が可能となる。このレーザー加工装置は,同社製の大型フォトマスクブランクスを用いたフォトマスクと独自の特殊レンズの組み合わせで,□100mm以上の面積を連続で加工することができるとしている。

加工時間は1パッケージ基板の大きさによって変わるが,配線パターンと電極パッドの加工時間と,ビアの加工時間は同じでビア加工時間はビア数に依らない。一例として,2μm溝幅で深さ5μmのトレンチと,直径10μmで深さ5μmの電極パッドを,515mmx510mmの有機基板上に加工するのに必要な時間も,その後上径7μm/下径5μm/深さ5μmのビア加工をする時間も同様におおよそ20分程度で完了するという。