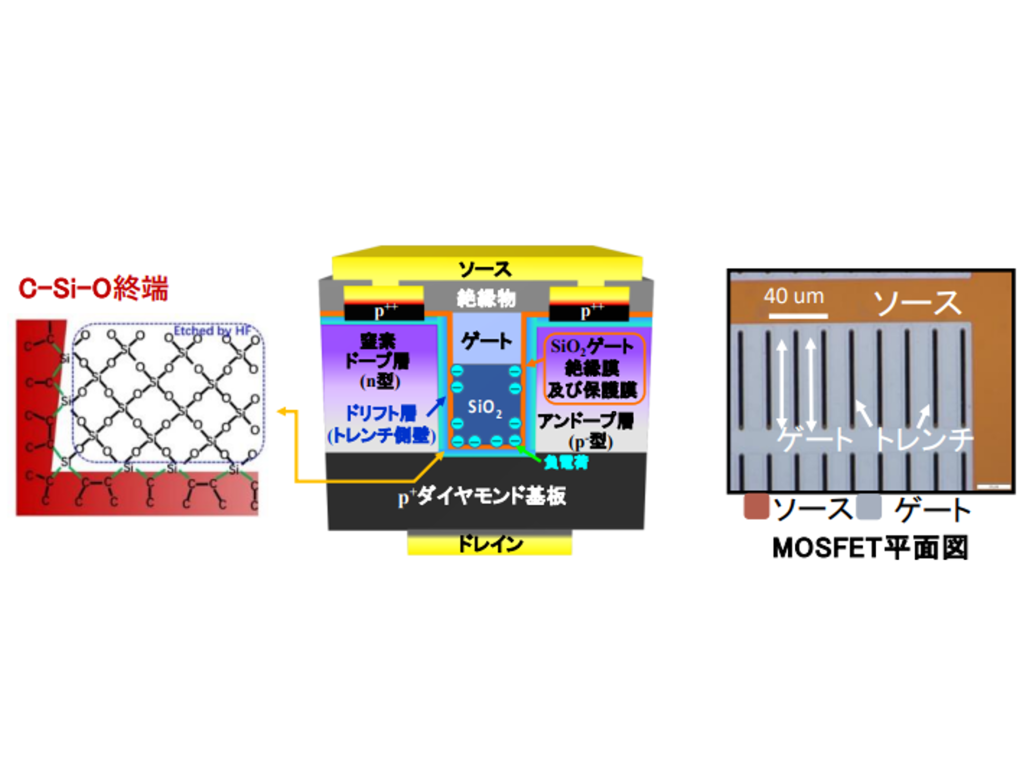

次世代ダイヤモンド半導体パワーデバイス・高周波デバイスの研究開発を行なうPDSと早稲田大学は,チャネル移動度(ホール)150cm2/V·s,閾値電圧3~5V程度の酸化シリコン終端(C-Si-O終端)構造によるノーマリ・オフ型ダイヤモンドMOSFETを開発した(ニュースリリース)。

水素終端構造を用いたダイヤモンドMOSFETの研究開発は世界中で行なわれているが,2DHG(2次元ホールガス)の存在により,基本的にノーマリ・オン(ゲート電圧が0Vのときにトランジスタがオン状態)動作になる。

パワーエレクトロニクス応用を想定した場合,フェールセーフ(正常な動作がしなくなったときに安全な状態で停止させるアプローチ)の観点から,一般的にノーマリ・オフ(ゲート電圧が0Vのときにトランジスタがオフ状態)動作が望まれる。この課題に対し,PDSは,パワーエレクトロニクス応用を見据え,酸化シリコン終端構造によるノーマリ・オフ化技術の開発を進めてきた。

横型の酸化シリコン終端構造ダイヤモンドMOSFETの最大ドレイン電流は300mA/mm以上,縦型の酸化シリコン終端構造ダイヤモンドMOSFETの最大ドレイン電流は200mA/mm以上を達成し,いずれもノーマリ・オフ型ダイヤモンドMOSFETの最高値だという。さらに,チャネル移動度(ホール)は,次世代半導体として社会実装が進むSiCに匹敵する値が得られた。

また,表面をC-Si-O結合で覆うことで従来のC-H表面に比べて,高温や酸化に強い安定なデバイスとなったと考えているという。C-Si-O表面は,SiやSiCの表面と同様で,製造工程でSiやSiCと同様の手法が使え,量産性にも適している。

PDSは,ダイヤモンド半導体の普及,実用化に向けたダイヤモンドMOSFETの研究開発を強化していくとしている。