東北大学と技術コンサルタントのCUSICは,3C-SiCと4H-SiCを積層させたハイブリッド構造基板を同時横方向エピタキシャル成長法を用いて製作することに世界で初めて成功した(ニュースリリース)。

SiCの単結晶基板を用いたパワー半導体デバイスの実用化が世界中で進められている。しかし,電力損失低減や長期信頼性の観点では,基板として用いるSiC単結晶の持つ物性そのものに由来する根本的な問題点があった。

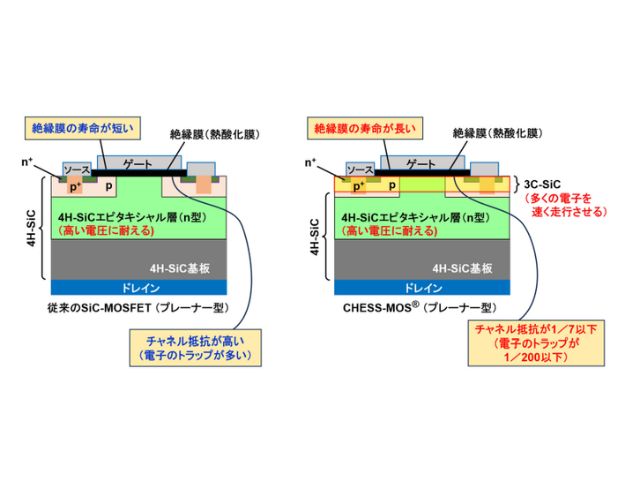

CUSICは,SiCパワー半導体デバイスの電力損失低減と長期信頼性確保を同時に実現する技術として,新しいパワー半導体デバイス「CHESS-MOS」を考案した。これは,同じ SiC 単結晶でありながら異なる結晶構造・物性値を持つ3C-SiCと4H-SiC を積層させたハイブリッド構造基板によって実現したもの。

3C-SiC 層には“長期にわたって安定的に多くの電子を速く走行させる役割”,4H-SiC 層には“高い電圧に耐える役割”を割り当てることで,電力損失低減と長期信頼性の両立を可能とするが,その実現には,3C-SiCと4H-SiCを結晶格子をシームレスに積層させる基板加工技術と結晶成長技術が不可欠だった。

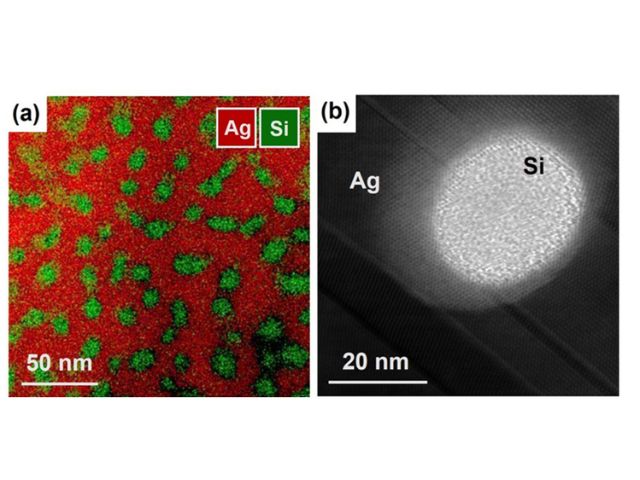

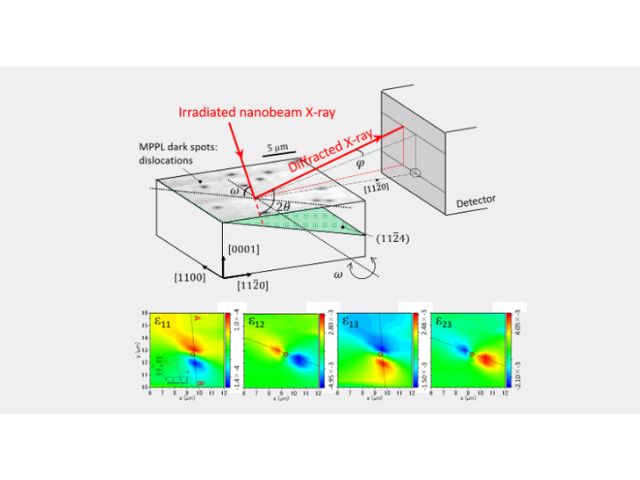

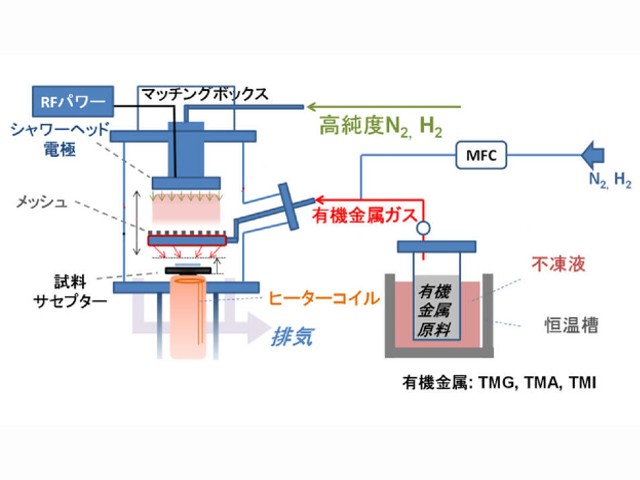

研究グループは,3CSiCと4H-SiCを積層させたハイブリッド構造基板を同時横方向エピタキシャル成長法(SLE法)を用いて製作することに世界で初めて成功した。

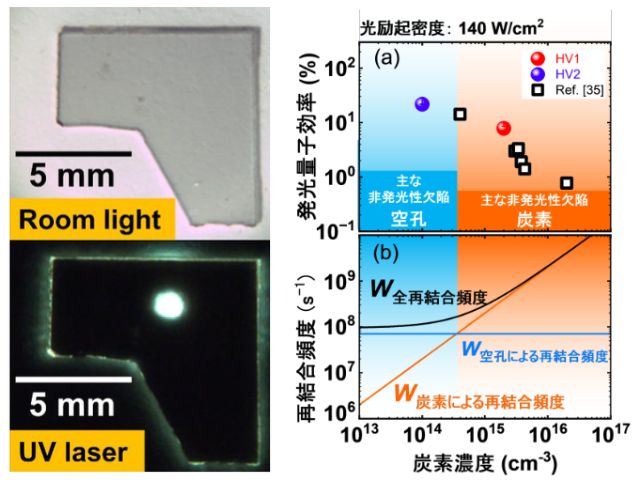

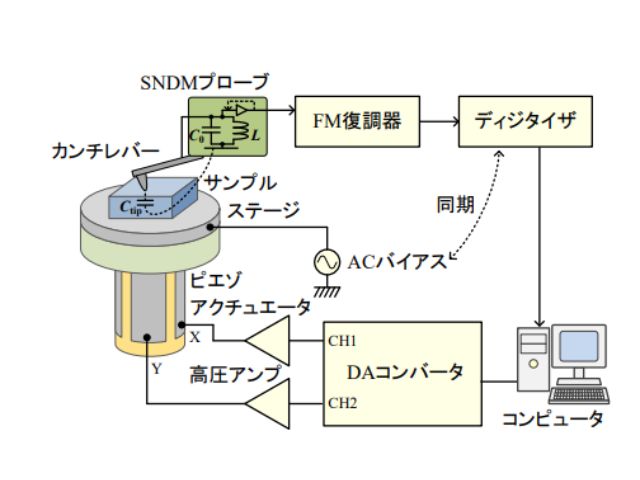

さらに,絶縁膜(熱酸化膜)を形成したハイブリッド構造基板表面の界面準位密度を走査型非線形誘電率顕微鏡法(SNDM法)によって計測した所,3C-SiC表面の密度は4H-SiC表面の200分の1以下となり,SLE法によって界面準位密度を大幅に低減できることを実証した。

これまでの知見から,こののような低い界面準位密度が達成されれば,CHESS-MOSを取り入れることにより,電力損失が30%以上削減できる見通しとなるという。

さらに,二重量子井戸構造の形成を確認したころから,高周波デバイス・高周波集積回路の実現の可能性が示された。

研究グループは,SiCパワー半導体デバイスを用いたシステムの高性能化・新機能創出と省エネルギー化の両立に大きく貢献することが期待される成果だとしている。