半導体ソフトエラー評価を可能にする技術を開発京都工芸繊維大学の研究グループは,様々な中性子施設で半導体ソフトエラー評価を可能にする技術を開発した(ニュースリリース)。

半導体ソフトエラー評価を可能にする技術を開発京都工芸繊維大学の研究グループは,様々な中性子施設で半導体ソフトエラー評価を可能にする技術を開発した(ニュースリリース)。

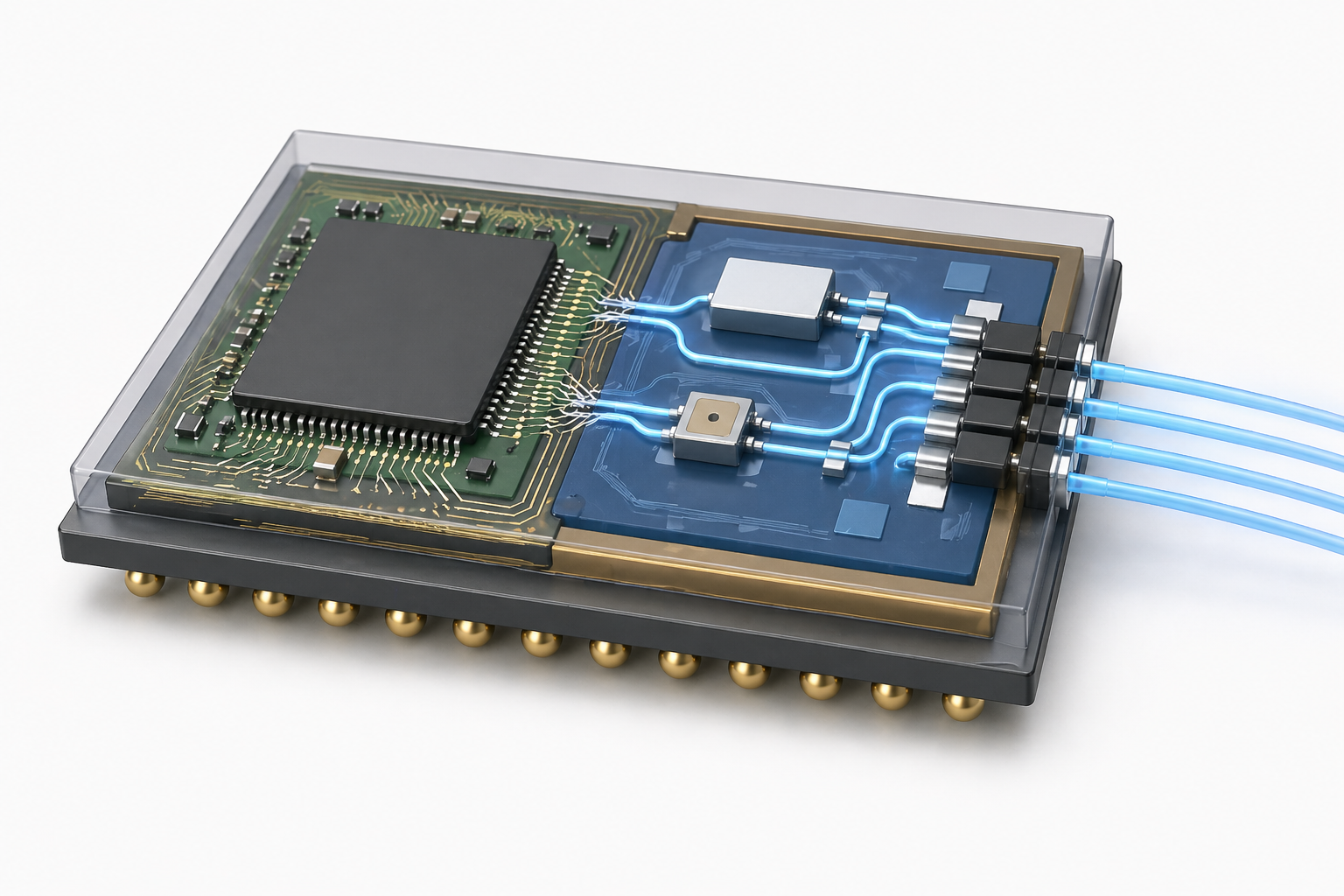

地上には宇宙線が空から降り注いでおり,そこに含まれる中性子によって半導体チップにソフトエラーと呼ばれる事象が生じ,その結果としてコンピュータが誤作動を起こすことが知られている。

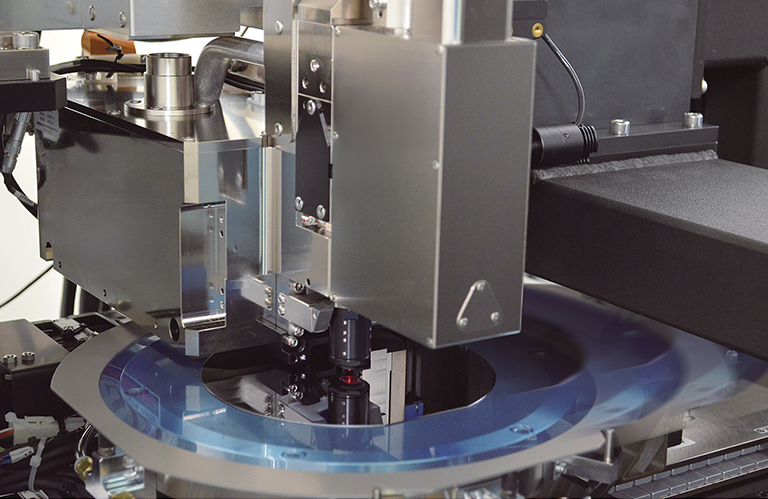

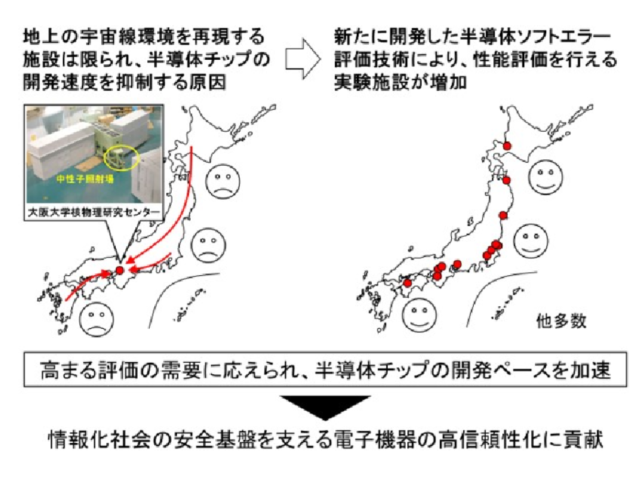

ソフトエラー率は,地上の宇宙線環境を再現する特殊な中性子源を用いた実験で評価する方法が一般的だが,そのような中性子源は国内で1つ,世界でも5つほどしかなく,年々高まる半導体チップのソフトエラー率評価の需要を満たすには限界があった。

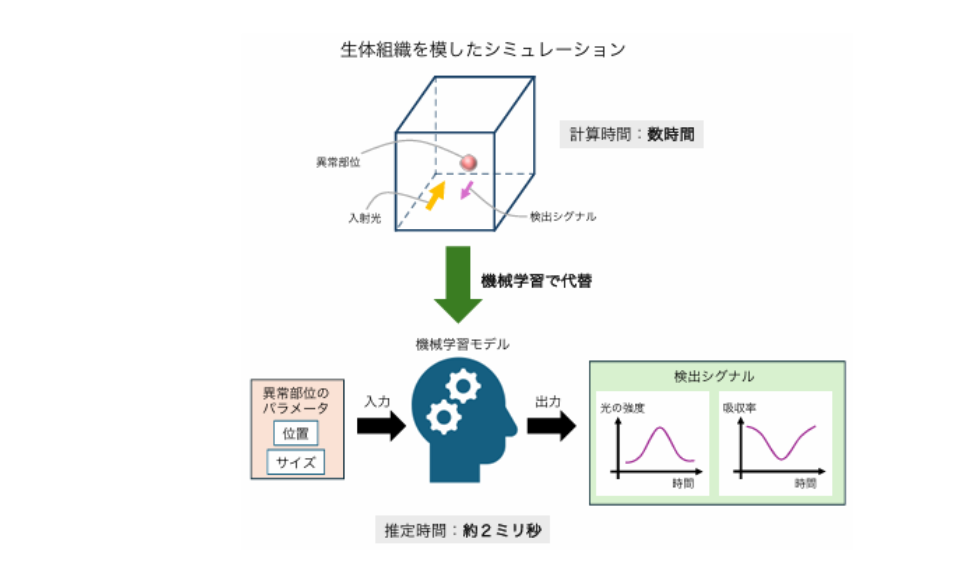

今回研究グループは,様々な中性子施設でソフトエラー測定実験を行なうとともにPHITSシミュレーションによる解析を行ない,任意の中性子源による1つの測定結果とシミュレーションを組み合わせることにより,地上ソフトエラー率を求める手法を開発した。

半導体チップのソフトエラー発生確率は中性子のエネルギーとエラー発生に必要なノイズ電荷量(Qfit)によって異なる。測定に用いた中性子源のエネルギー分布,シミュレーションによって求めたソフトエラー発生確率を用いて,測定結果を再現するQfitを求める。

Qfitが求まると,ソフトエラー発生確率と中性子のエネルギーの関係が分かるので,地上の中性子エネルギー分布と組み合わせて計算することで,地上のソフトエラー率を求めることができるという。

65nm設計ルールの1V動作SRAM(Static RAM)を用いた実験で,用いた中性子源によるソフトエラー率の違い(最大値と最小値の比)が,2倍以内に収まることを確認した。この研究成果により,世界中に多数ある中性子源を活用して半導体チップのソフトエラー率の評価が可能となるとする。

研究グループは今後,開発した手法を最先端の半導体チップに応用するため,65nmよりも微細な製造プロセスで製造された半導体チップでも同様の評価が可能であることを確認するとともに,開発した評価手法が世界標準規格と策定されるように標準化機関に働きかける。

高まる半導体チップのソフトエラー率評価の需要に応え,高信頼な半導体チップの設計やそれを用いた情報システムの高信頼化に貢献するとしている。