横浜国立大学,ディスコ,東レエンジニアリングは,直接接合技術を用いた,新規なチップ仮接合および剥離技術の開発に成功した(ニュースリリース)。

横浜国立大学,ディスコ,東レエンジニアリングは,直接接合技術を用いた,新規なチップ仮接合および剥離技術の開発に成功した(ニュースリリース)。

半導体デバイスの微細化限界を突破し,高性能化・低消費電力化を目指す手法として「チップレット集積」が大きな注目を集めている。しかしチップをウエハー上に接合し垂直方向の電気的な接続を担保する接合/配線技術に課題が残っており,新たな接合手法や集積手法が求められている。

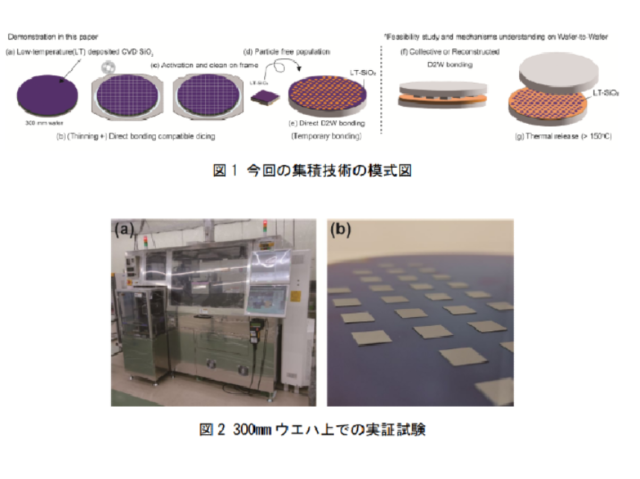

研究では新たに開発したCVD絶縁膜を用いて,チップをウエハー上に仮接合する方法を示した。このアプローチでは,仮接合はプラズマ活性化ダイレクトボンディングによってな行なわれる。

したがって,仮接合界面はほとんどの前工程プロセスと互換性があり,先端ファブの技術を用いたさらなる微細化など,拡張性の見込める集積技術だという。

さらに,界面層が薄く固体であるため,ボンディング中のダイのずれのリスクを軽減することができる。これによってDie-to-Waferの「ハイブリッド接合」を可能とし,仮接合による材料の加工時間,材料損失を削減,低コスト化が実現可能になる新規な垂直方向配線形成技術及びチップ集積技術だとする。

仮接合の鍵は,低温で堆積されたSiO2膜による意図的なボイドの形成と制御された接合エネルギー。これらを達成するための表面粗さ,膜組成,機械的特性,およびプラズマ活性化の影響を詳細に調査した。

さらに,メカニズムの解明を目的として界面解析(例:無水雰囲気でのボンディングエネルギー測定,界面空孔検査,TEM分析)を行なった。

TDSと陽電子消滅分光法(PAS)の組み合わせにより,低温で堆積されたSiO2には多くのオープンスペースと水が内部に含まれており,水の貯蔵層として機能し,ポストボンドアニール中に放出される可能性があることが明らかになった。これによって熱剥離が可能となり,非常に低い力で簡単にウエハとチップが剥離可能だとする。

この集積技術は300mmウエハー上にてデモンストレーションも行なった。研究グループは,この新たな仮接合技術により,歩留まり向上,高いボンディング位置合わせ精度,およびコスト削減を伴う高度な異種3D集積が可能になるとしている。