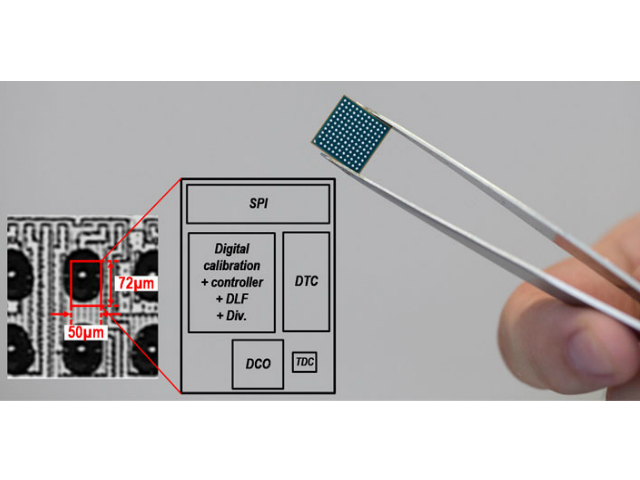

東京工業大学,ソシオネクストの研究グループは,最先端の5nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功した(ニュースリリース)。

東京工業大学,ソシオネクストの研究グループは,最先端の5nm FinFET CMOSプロセスで世界初となる世界最小の高性能分数分周型クロック回路の開発に成功した(ニュースリリース)。

この成果は,従来のデジタルPLL(クロック回路)において,アナログ回路構成で実現されていたデジタル制御発振器(DCO)および時間差デジタル変換器(TDC)をデジタル回路構成により実現できたことによるもの。

従来のデジタルPLLでは,TDC回路で長い時間差の変換が必要だったため,アナログ回路設計による高線形なTDCが必要だった。この研究成果では,タイミングをデジタル的に制御するデジタル時間変換器(DTC)とTDC回路とを組み合わせることで,TDC回路に必要な時間差範囲を狭めることに成功し,そのデジタル回路化に成功した。

一方で,DTC回路には長い時間差での変換が必要になるが,デジタル補正を組み合わせることでこの問題を解決した。DCO回路においても,同様にデジタル補正を駆使することでデジタル回路化を実現した。

以上により,PLL回路全体をデジタル回路として構成することが可能となり,デジタル回路開発で使用されている回路合成・タイミング設計や自動配置配線ツールを活用できるようになり,通常のデジタル回路同様に,PLLをスタンダードセルによって自動設計できるようになった。これは異なるプロセス間での移植性を高め,新たに開発された最先端製造プロセスにおいても迅速な回路設計を可能とする。

実現した回路は,分数分周型(フラクショナルN型)のPLLで,わずかな面積で高周波信号の生成が可能なリングオシレータ型の発振器を用いた。回路面積は世界最小の0.0036mm2であり,消費電力とジッタ特性に関する性能指標であるFoMが-235dBと,極めて優れた性能を達成した。わずか0.95mWの消費電力で動作し,スプリアスレベルは低く-44dBcであった。さらにスペクトル拡散クロック機能を有し,低電磁妨害特性を実現した。

今回の高性能クロック回路により,世界最先端の5nmプロセスによる高性能,低消費電力,小面積のSoCを短期間で設計することが可能になった。ソシオネクストは今回の成果をもとにAIやIoTなど今後も継続して市場の成長が予想される分野で商品やサービスの差異化に寄与するSoCを供給していくという。

また研究グループは今後も,アナログデジタル変換器などの他の種類のアナログ回路の自動合成を始めとするCMOSミックストシグナル設計の基礎技術開発の分野で協力していくとしている。