東京大学の研究グループは,半導体へテロ構造を用いて,高効率な冷却素子を開発した(ニュースリリース)。

現在,膨大なデータを超高速に扱うデータセンターやスーパーコンピューターなどでは高効率にデバイスを冷却する技術の開発が急務となっている。

従来,熱電効果を用いたペルチェ素子が,ほぼ唯一の実用的な固体冷却素子だったが,ペルチェ素子内では,電子は頻繁に散乱を受けながら伝導するため,低い冷却効率しか得られない。

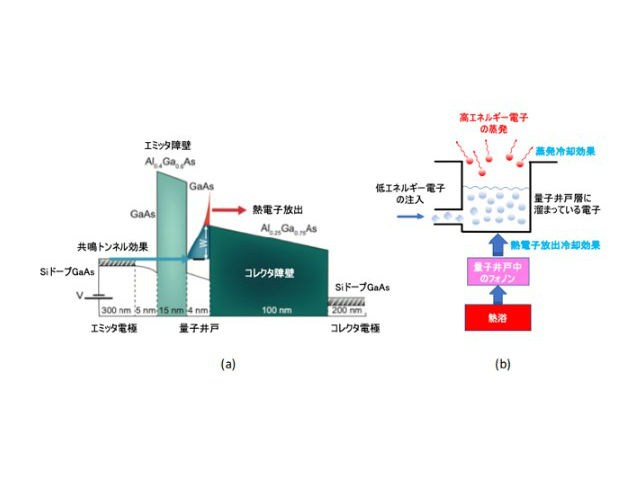

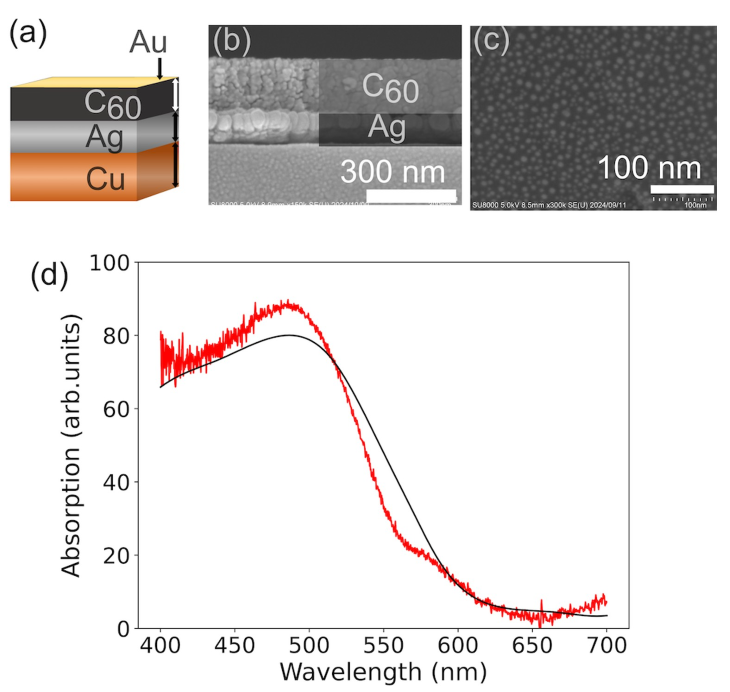

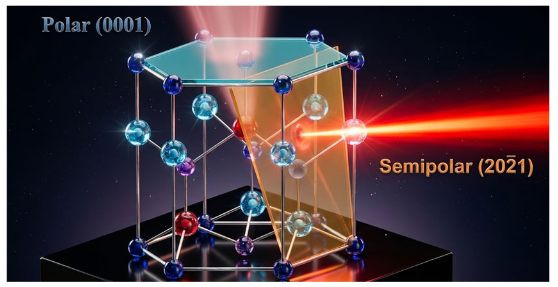

今回研究グループが開発した素子構造は,薄くてエネルギー障壁が高い障壁層(エミッタ障壁)を介して,電子が共鳴トンネル効果により量子井戸層に注入される。

注入された電子は,量子井戸層内で熱的な分布を取るが,量子井戸層を出るときには,低くて厚い障壁(コレクタ障壁)の高さ以上のエネルギーを持つ高エネルギーの熱電子のみが超えていく過程で電子が伝導し,電流を流すにつれて量子井戸層内の電子系からエネルギーが奪われていき,電子系の温度が下がる(蒸発冷却)。

このとき,電子系と熱的に接している量子井戸内の結晶格子系とが相互作用し,格子系も冷却されていく(熱電子放出冷却)。この素子構造では,数nm程度の半導体超薄膜内に冷却効果が発生するため,極薄膜中の温度を精密に測定する技術の開発が必要となる。

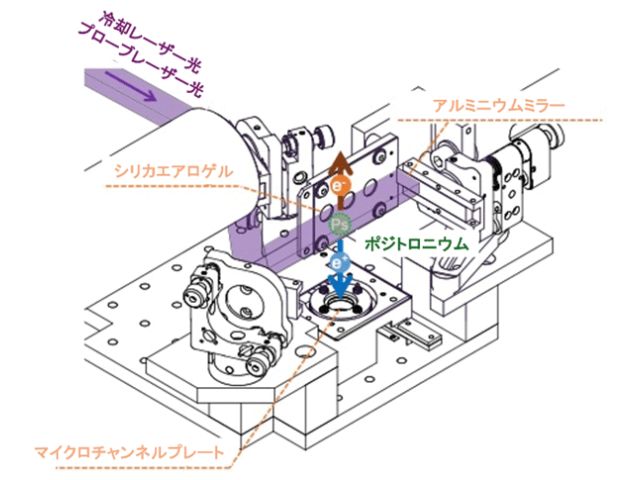

研究グループは,量子井戸内の電子系の温度を評価する方法として,フォトルミネッセンス分光法に注目し,フォトミネッセンスピークの高エネルギー側のスペクトル形状から電子系の温度(電子温度)を評価する実験を行なった。

作製した非対称二重障壁半導体ヘテロ構造にレーザー光を照射し,電圧の関数として素子からのフォトミネッセンスを測定した。さらに,フォトミネッセンスのスペクトルの高エネルギー側の裾野の傾きをマックスウェル分布を仮定してフィッティングを行なうことにより,電子温度をバイアス電圧の関数として求めた。

その結果,バイアス電圧の印加によらず電極内の電子温度はほぼ室温で一定であるのに対して,量子井戸からの発光においては,バイアス電圧の印加とともにスペクトルの裾野の傾きが急になり,電子温度が300Kから250Kまで約50Kも低下することがわかった。この結果は,研究グループが行なった熱非平衡な電子・格子系を取り扱う詳細な理論計算ともよく一致したという。

研究グループは,この素子はトランジスタや半導体レーザーなどのデバイス活性層を局所的に高効率に冷却する新しい素子技術として,省エネルギーに大きく貢献することが期待できるとしている。