東京大学は,8nmの金属酸化物半導体IGZOをチャネルとしたトランジスター型強誘電体メモリー(FeFET)の開発に成功した(ニュースリリース)。

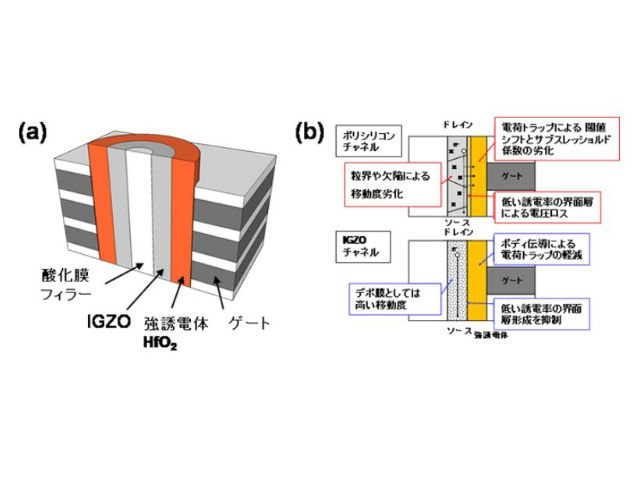

強誘電体二酸化ハフニウム(HfO2)をゲート絶縁膜としたFeFETは,低消費電力で大容量なメモリーデバイスとして注目を集めているが,シリコンをチャネルとするデバイス構造の場合,誘電率の低い界面層が形成されてしまい,界面層への電圧降下と電荷トラップが起こるため低電圧動作と高信頼性動作を同時に実現することが困難だった。

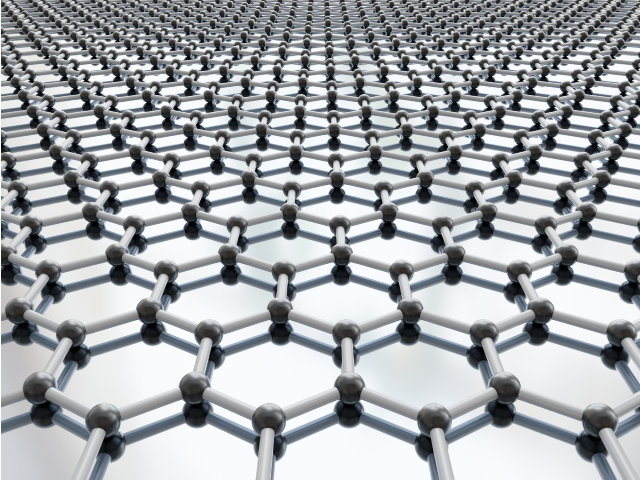

今回の研究では,界面層の形成と電荷トラップの影響を抑制し,3次元積層構造でも高い読み出し電流を得るために,金属酸化物半導体IGZOをチャネルとする強誘電体HfO2ゲート絶縁膜FeFETを提案した。このデバイス構造を用いると,IGZOと強誘電体HfO2の間で誘電率の低い界面層の形成を抑えることができる。

さらにN型にドープされているIGZOをチャネルにすることでジャンクションレストランジスターとして動作し,キャリヤーは界面でなくボディ(チャネル中央部)を流れるため,キャリヤーの電荷トランプを抑制することが可能。

ジャンクションレストランジスターがノーマリーオフ動作,つまりゲート電圧がゼロの時に電流が流れないようにするには閾値電圧を制御する必要があり,IGZOの膜厚を10nm以下にした。10nm以下の膜厚では,ポリシリコンの移動度は10cm2/Vsよりも低くなってしまうが,IGZOであれば10~100cm2/Vsの高い移動度を維持することができるという。

デバイスプロセスの開発ではまず,IGZOの膜厚の最適化を行なった。IGZOをチャネルとし,二酸化ケイ素(SiO2)をゲート絶縁膜とする通常のMOSFETを作製してサブスレッショルド係数と閾値電圧の膜厚依存性を調査したところ,膜厚を薄くするにつれてサブスレッショルド係数が小さくなり,閾値も負から正に変化することがわかった。最終的に8nmの膜厚が最適値となり,サブスレッショルド係数は理想的な60mV/decで,閾値電圧も正となりノーマリーオフ動作することがわかった。

次にIGZOをチャネルとした場合に,ゲート絶縁膜であるHfO2が強誘電性を示すかを調査した。その結果,強誘電体の特徴を示す残留分極は30μC/cm2と極めて大きな値を示し,IGZOチャネル上に強誘電体HfO2が形成できることを明らかにした。

今回の技術により,8nmの膜厚のIGZOをチャネルとする強誘電体HfO2ゲート絶縁膜FeFETを作製したところ,サブスレッショルド係数は理想的な60mV/dec,メモリーウィンドウは0.5V以上の高移動度で低電圧動作可能な優れたメモリー特性を実現した。研究グループは,この技術によりIoTデバイスのエネルギー効率が飛躍的に向上するとしている。