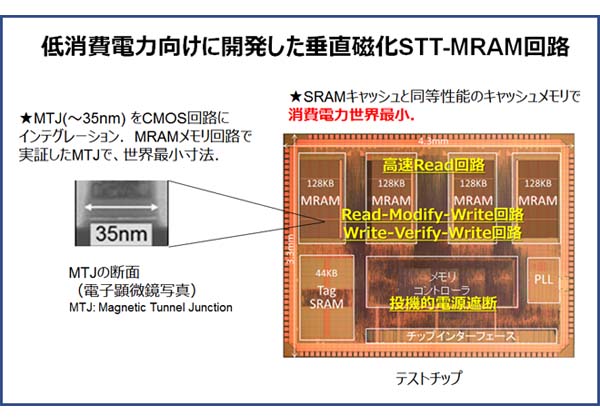

新エネルギー・産業技術総合開発機構(NEDO)のプロジェクトにおいて,東芝と東京大学は,コンピュータのキャッシュメモリー用に十分な高速性能を有し,従来の混載メモリー(SRAM)と比較して消費電力を10分の1以下の4Mビットクラスの新方式磁性体メモリー(STT-MRAM)回路を開発した(ニュースリリース)。

新エネルギー・産業技術総合開発機構(NEDO)のプロジェクトにおいて,東芝と東京大学は,コンピュータのキャッシュメモリー用に十分な高速性能を有し,従来の混載メモリー(SRAM)と比較して消費電力を10分の1以下の4Mビットクラスの新方式磁性体メモリー(STT-MRAM)回路を開発した(ニュースリリース)。

近年,様々な用途の半導体SoCの高性能化と低電力化のニーズが高まる中,超低消費電力化の実現を目指し,NEDOは「ノーマリーオフコンピューティング基盤技術開発」プロジェクトを推進している。これは,不揮発性メモリを利用して,コンピュータの非動作時に積極的に電源をオフして省電力化を図るもの。

しかしながら,コンピュータのキャッシュメモリに使われるSRAMのような高速メモリーは揮発性メモリーのため,データの保持を考えると電源オフができない。一方で,今までの不揮発性メモリーでは高速化が実現できていなかった。

現在キャッシュメモリーとして利用されている揮発性メモリー(SRAM)に代わる,高速で低消費電力の不揮発性磁性体メモリー(MTJ:Magnetic Tunnel Junction)の開発を続けてきたが,メモリー制御回路部(周辺回路)が消費する電力が大きいため,不揮発性メモリーのみの低消費電力化を実現してもキャッシュメモリー全体としての消費電力は十分に小さくならなかった。

今回,研究グループは,65nm世代のシリコントランジスタに混載した4Mビットクラスの新方式磁性体メモリー(STT-MRAM)回路において,3.3nsというキャッシュメモリーとして十分に高速なアクセス時間,ならびに揮発性メモリー(SRAM)と比較して消費電力10分の1以下という低消費電力化を実現した。これは,キャッシュメモリーとして世界最高の電力性能となるもの。

今回,メモリー制御回路部をノーマリーオフ動作状態に近づけるため,100ns以下で高速に電力遮断・復帰が可能な回路を開発し,メモリー動作状態に応じて動作に必要な部分以外は高速で電源遮断できるように改良した。

主な動作モードでの実測値として,キャッシュメモリーアクセスの平均待機時間(約30ns)よりも短い,最速22nsで電源遮断後からの復帰を確認している。

また,メモリーのデータを一度確認して不要な書き込みを止めることで書き込み動作の消費電力を削減する技術を採用した。さらに,電源を遮断できる時間をできるだけ長くするために,メモリーアクセスパターンをモニターして,次のアクセスパターンを高い正解率で予測するアルゴリズムも開発した。

さらに,これらの技術により,従来の揮発性メモリー(SRAM)と比較して消費電力を10分の1以下にまで削減することができた。

関連記事「東工大,三次元積層メモリーの厚さ1/10に」「産総研,電圧書込みメモリーの動作・エラー率評価に成功」「中大,CNTを使った半導体メモリNRAMの・高速・低電力・高信頼な基本動作を実証」「東大ら,低エネルギーメモリにつながる量子臨界性をキラルスピン液体に発見」