東京大学の研究グループは,グラフェンに類似した原子層物質の一種である二硫化タンタルの超薄膜が,次世代不揮発性メモリー「メモリスタ」として機能することを発見した(ニュースリリース)。

東京大学の研究グループは,グラフェンに類似した原子層物質の一種である二硫化タンタルの超薄膜が,次世代不揮発性メモリー「メモリスタ」として機能することを発見した(ニュースリリース)。

現在,脳内の情報処理の仕組みを模倣する脳型コンピューターの開発が始まっている。脳内の神経回路は,ニューロンと呼ばれる細胞と,ニューロン間をつなぐシナプスと呼ばれる部位から構成される。情報の入力頻度が多いと,シナプスが変化しニューロン間の結合が強まって,情報が記憶される。逆に入力頻度が少ないと,結合が弱いままで情報は忘却される。

脳型コンピュータを実現するには、ニューロンとシナプスに対応した電子素子が必要となる。そこでシナプス素子として,「メモリスタ」と呼ばれる次世代不揮発性メモリが注目されている。電圧を加える回数を増やすたびにメモリスタの抵抗値が段階的に変化し,各中間的な抵抗値が電圧を遮断しても保持されるという,多値の不揮発性メモリーとしてメモリスタは動作する。

脳型コンピューターにおいてメモリスタはニューロン素子間に接続され,メモリスタへ電圧を加えることがシナプスへの情報の入力に対応する。電圧を何度も加えると,ニューロン素子間の電気の流れやすさが徐々に変化するが,これは情報が高頻度に入力されてニューロン間の結合が強くなることに対応する。

2008年に初めてメモリスタが開発されたが,その後,研究はあまり発展していない。従来型のメモリスタは酸化物の多層膜構造を有し,電圧印加に伴う原子配置の変化を利用して動作する。メモリスタの研究開発を活性化させるためには,従来型とは異なる材質,構造の,全く新しいメモリスタの形を提示する必要があった。

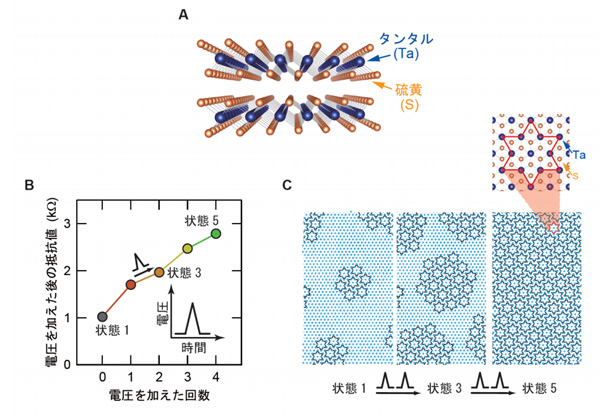

研究グループは,グラフェンのような層状構造を有する物質の超薄膜である新規ナノ材料「原子層物質」の一つ,二硫化タンタル(TaS2)の超薄膜に着目した。タンタル(Ta)と硫黄(S)の原子層から構成されるTaS2超薄膜をシリコン基板上に用意し,超薄膜上に電圧印加及び抵抗測定用の電極を設置して,素子を完成させた。超薄膜の厚みは7~100㎚,大きさは数μm角程度。

実験では,素子に4ボルトの電圧を短時間加える操作を繰り返した。すると,電圧を加える回数を重ねるごとに,抵抗値の増加が観測された。すなわち,素子は電圧印加の履歴を記憶していることになる。さらに,電圧印加が終了するたびに抵抗値の経時変化を追跡したところ,各電圧遮断後の抵抗値がほとんど変化しなかった。

つまり電圧を遮断した後の各状態は,いずれも不揮発な状態であり,素子は多値の不揮発性メモリーとして動作していることから,メモリスタと言える。

このメモリスタ動作は,TaS2超薄膜において生じる電子の相転移を利用している。TaS2の超薄膜は,多数の電子が自由に動ける低抵抗な準金属的状態,動けない高抵抗な絶縁体的状態,さらに一部の電子が動ける複数の中間的状態の間を相転移することが分かった。過冷却状態の水に振動を加えると氷になるように,TaS2超薄膜に電圧を加えることが刺激となって,異なる状態間を行き来できていると考えられるという。

今回実現したメモリスタは,動作原理や材料の点で従来型メモリスタと一線を画しており,メモリスタ研究開発の上での新たな試金石になりえるとする。研究で達成した構造の簡単化は,製造コストの低化や集積度の向上に直結するものであり,シナプス素子の高密度実装が必要な脳型コンピューターの実現を後押しするものだとしている。

また今回採用した原子層物質は,現在ポストシリコン・ポストグラフェン材料として注目されているナノ材料であることから,研究グループは今回の研究が原子層物質の未知の潜在能力を再認識する契機となり,原子層物質の研究を促進する効果も期待している。

関連記事「東工大ら,継続した刺激でシナプスが減ることを発見」「阪大,シナプスの形成位置と老化に伴う動体視力低下の関連を解明」「東大ら,過剰に生成されたシナプスが選別される「シナプス刈り込み」のしくみを解明」「パナソニック,CMOSを用いたニューラルネットワーク回路を開発」