米IBMは,生成AIモデルの学習・推論の効率を向上する可能性がある光電融合技術の一つである光パッケージング技術,Co-Packaged Optics(CPO)の新しいプロセスを開発し,データセンター内の電気配線を補完する光技術の導入を可能にしたと発表した(ニュースリリース)。

現在,データセンターのラック間の通信は依然として電気配線で行なわれている。電気配線はGPUアクセラレーターに接続されるが,GPUアクセラレーターは半分以上の時間はアイドル状態であり,大規模な分散学習プロセス時には他のデバイスからの信号を待つため,膨大な費用とエネルギーを消費する。

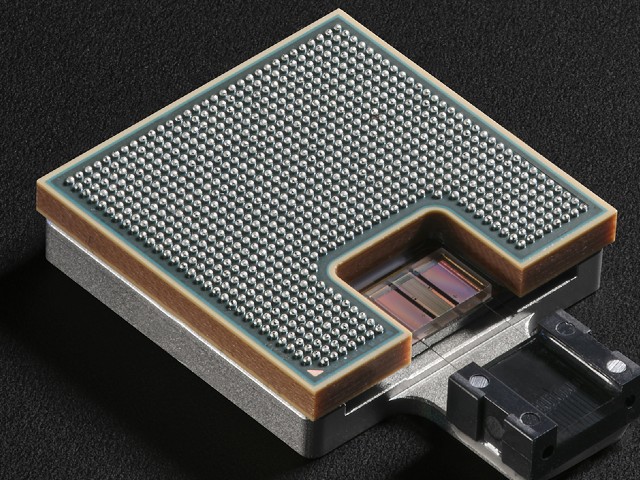

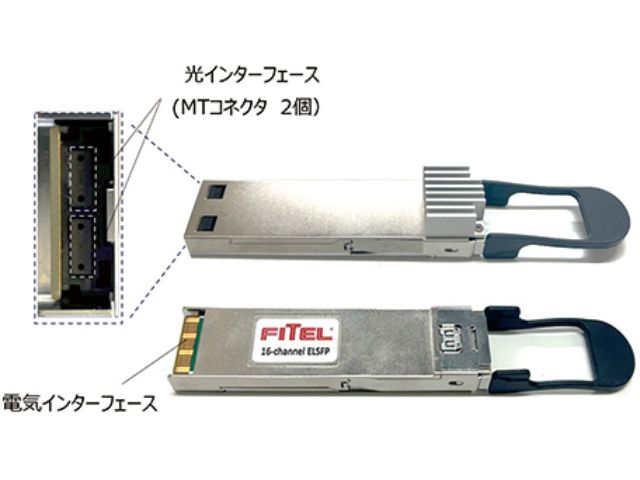

今回同社は,新しいCPOプロトタイプ・モジュールを開発した。この技術は,データセンター内の通信の帯域幅を大幅に拡大し,GPUのアイドリング・タイムを最小化しながら,AIの処理能力を大幅に向上させる可能性があるという。

これにより,ミッドレンジの電気配線と比較して消費電力は1/5以下になり,従来の電気配線と比較して最大5倍高速に大規模言語モデル(LLM)を学習でき,より大規模なモデルとより多くのGPUを使用してパフォーマンスの向上を図れるとする。

さらに,1つのAIモデルの学習ごとに,米国の5,000世帯の年間消費電力に相当する電力を節電できるだけでなく,今後はチップ間でも光通信が可能になるという。

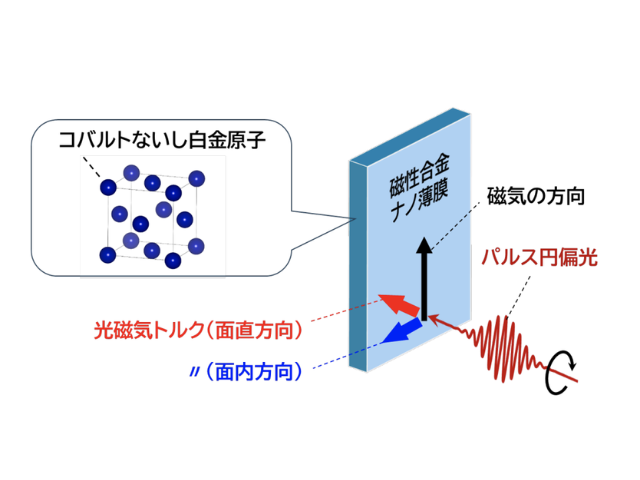

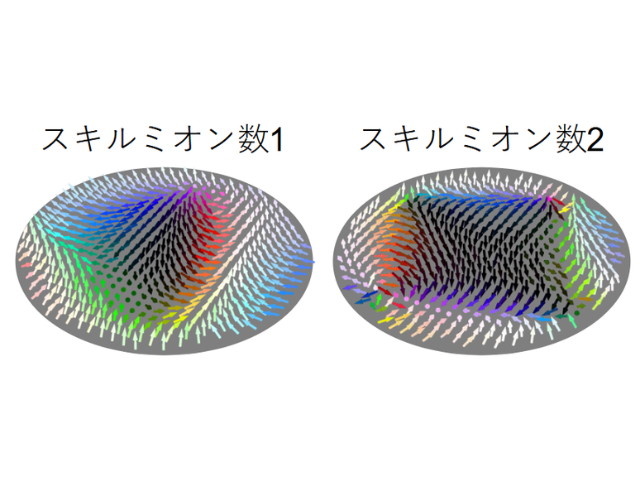

CPOは,チップメーカーがアクセラレーター間に光通信用配線を施すことで,アクセラレーター間のインターコネクト密度の拡張を目指している。同社では,この高密度光通信構造に光波長多重通信技術を組み合わせることにより,電気配線と比較し,チップ間通信の帯域幅が最大80倍向上する可能性があるとしている。

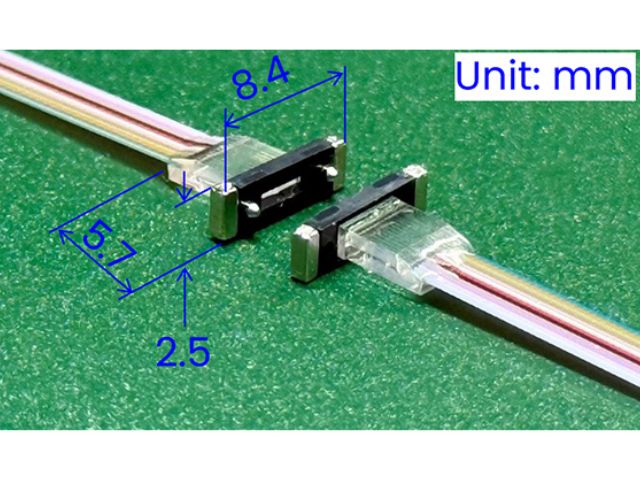

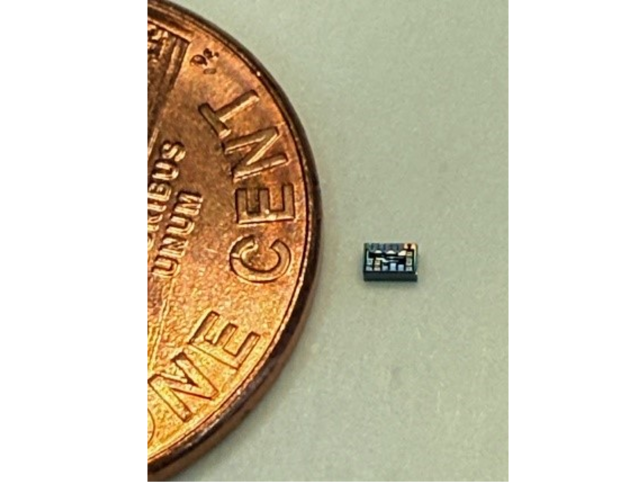

現在の最先端のCPO技術と比較して,チップメーカーはシリコン・フォトニクス・チップの端面に6倍の光ファイバーを配線できるようになる。各光ファイバーは,人の髪の毛の約3倍ほどの幅で,長さは数cm~数百mに及び,数Tb/sのデータを通信する。

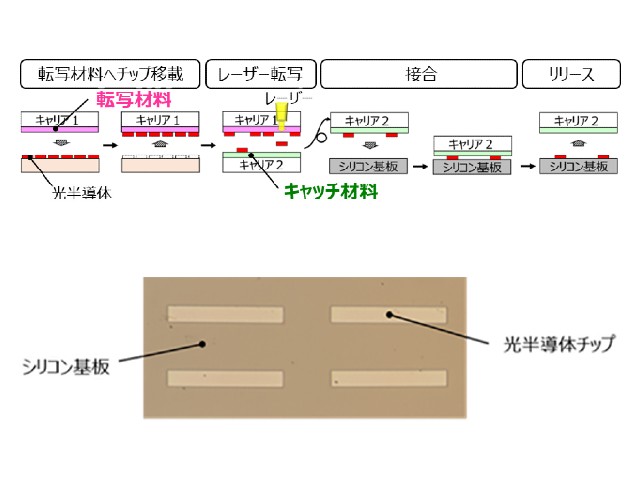

同社は,標準的なプロセスを用いて,50μmピッチの高密度のポリマー光導波路をシリコン・フォトニクス導波路にアディアバティック結合させた。このポリマー光導波路は,量産時に必要なストレス・テストに合格。コンポーネントは,-40°C~125°Cで動作し,機械強度テストにおいても合格した。さらに,18μmピッチの高密度のポリマー光導波路も実証した。4本のポリマー光導波路を積層することで,最大128チャンネルの接続も実現できるとしている。