東京工業大学と東京応化工業は,電子デバイスの高性能化を志向した10nm以下の半導体微細加工を可能にする高分子ブロック共重合体の開発に成功した(ニュースリリース)。

近年の人工知能やクラウドサービスの目覚ましい発展,スマートフォンなどの小型化および高性能化に伴って,電子デバイスに搭載される半導体チップのさらなる高性能化を実現する,より微細な加工技術の開発が重要な課題となっている。

フォトリソグラフィはトップダウン型の半導体微細加工技術の一つとなっている。現状の最先端技術として13.5nmの波長の光を用いるEUVリソグラフィが挙げられるが,従来の露光装置では得られる凹凸パターンの不均一さや線幅10nm以下の微細加工を成しえないことが課題となっている。

その課題を解決する目的で,現在,分子の自己集合により得られるナノ構造を用いるボトムアップ型の微細加工技術が注目されている。

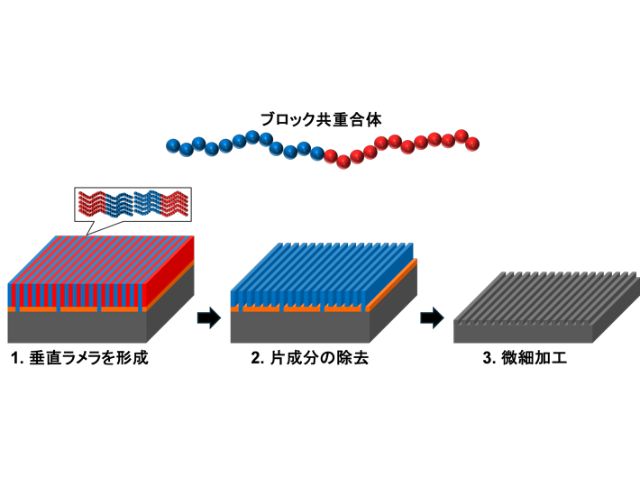

ボトムアップ材料としての利用が期待されている高分子ブロック共重合体は,異種の高分子鎖の末端同士が結合した特徴的な分子構造に起因して,分子の自己集合によりミクロ相分離構造と呼ばれるナノ周期構造を形成する。

ミクロ相分離構造はその周期長が5~100 nm程度であることから,半導体基板に回路パターンを描画するための鋳型としての応用が期待されている。

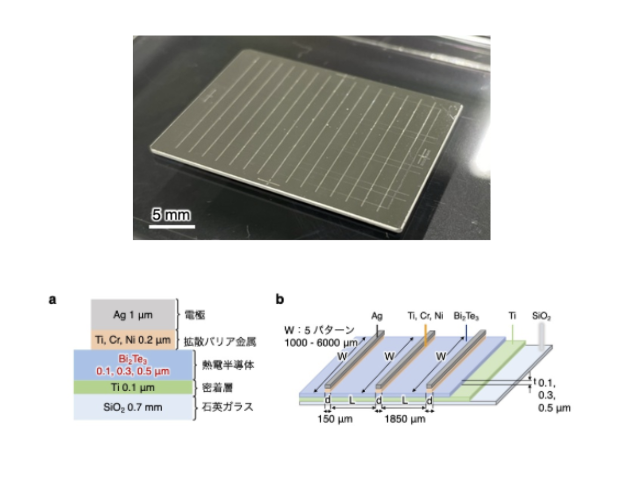

研究では,極性官能基の割合を精密に制御した分子設計と精密重合法での高分子の合成により,ポリスチレンの化学パターンに沿ってミクロ相分離構造を配列させた,新たな高分子ブロック共重合体を開発した。

この高分子ブロック共重合体は,シリコン基板上に薄く塗られた膜中に,回路パターンの線幅7.6nmに相当する線状構造を形成することが明らかとなった。この線状構造の線幅はEUVリソグラフィにより得られるパターン線幅の下限値よりも小さく,10nm以下の微細加工を可能とするもの。

研究グループは,半導体回路パターンのさらなる高解像度化と集積回路の高密度化が進み,電子デバイスの高性能化が加速することが期待される成果だとしている。