日本電信電話(NTT)は,超低遅延処理のための高性能な光論理素子を実現した(ニュースリリース)。

日本電信電話(NTT)は,超低遅延処理のための高性能な光論理素子を実現した(ニュースリリース)。

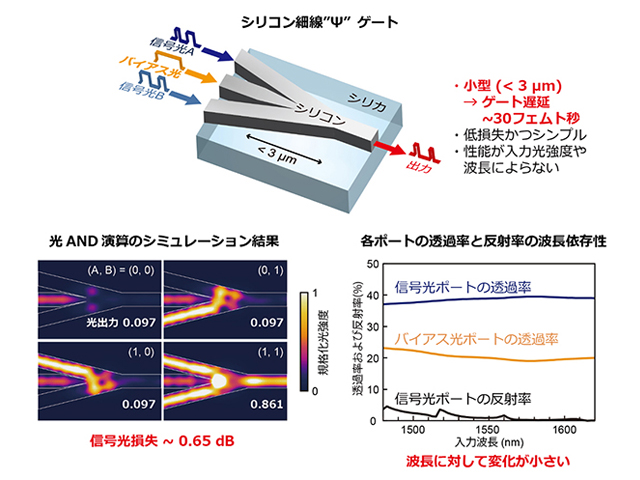

光回路の低遅延化は光信号がプロセッサ内をほぼ光速で伝わること以外にも,プロセッサ内の回路長をさらに短くする,つまり回路内の光ゲートの小型化により進展する。研究グループでは,ナノフォトニックプロセッサの要素技術である「ナノ受光器」,「ナノ光変調器」,またこれらの高度な組み合わせである「光トランジスタ」を実現してきた。

しかしながら,「光トランジスタ」のみにより光の低遅延性を損なわずに演算回路を組むことは容易ではない。そこで研究グループは,光の低遅延性に的を絞った光ゲートの開発を行なった。

今回,3つの同一波長の光波の入力を想定した干渉系において,2つの信号光AおよびBに加えて,演算を補助するもう一つの光,「バイアス光」を導入することで,様々な論理演算が入力光の位相およびバイアス光の振幅と位相の制御によって実現できることを見出した。バイアス光の入力振幅だけを変えるだけで,AND/XNOR/NORと機能が切り替えられる。

研究グループは,ギリシャ文字の“Ψ”と似た形状の,およそ3µm長のシリコン細線Ψゲートを見出した。この「シリコン細線Ψゲート」をチップ化し,20Gb/sの擬似ランダム光信号による実験を行なったところ,適切な振幅のバイアス光を入力することで2階調の明瞭なAND動作が観測された。また,バイアス光の入力強度を適切に増大したところ,XNOR動作およびNOR動作への動作の切り替えにも成功した。

同じ素子に対して,入力光の波長を1535から1565nmまで5nmずつ変更した計7波長におけるAND動作の結果を重ね合わせたところ,ほぼ波長無依存な動作が可能であることを確認した。これは,「波長チャンネルごとに独立した演算を同時に実行できる機能」(波長分割演算)が期待される結果となった。

これは非線形光学ゲートを用いた場合では実現がきわめて困難な動作の一つ。また,素子長(~3µm)から光AND演算に要する演算遅延はおよそ30fsと推測された。電子回路でのゲート遅延は10ps程度であるため,低遅延なことも分かったという。

研究グループは,近い将来,より低遅延かつ安全な情報通信を支えると共に,DNAシーケンスなどのビッグデータに対するパタンマッチング処理の高速化にも適用可能な技術としている。さらに,深層学習で話題のニューラルネットワークアクセラレーターにおいて,消費電力の90%を占める線形なベクトル演算もこのゲートで実施することで,低遅延かつ低消費になることが期待されるとしている。