産業技術総合研究所(産総研)は,独自に開発した単結晶酸化ガリウム(Ga2O3)の成膜プロセスを用いて,半導体Ga2O3をトンネル障壁層とした単結晶だけからなるトンネル磁気抵抗(TMR)素子を開発した(ニュースリリース)。

産業技術総合研究所(産総研)は,独自に開発した単結晶酸化ガリウム(Ga2O3)の成膜プロセスを用いて,半導体Ga2O3をトンネル障壁層とした単結晶だけからなるトンネル磁気抵抗(TMR)素子を開発した(ニュースリリース)。

メモリー機能をもつ縦型のスピン電界効果型トランジスタ(縦型スピンFET)は,電子スピンを利用することにより不揮発性のメモリー機能を得ることができるため,世界的に研究が行なわれている。しかし,メモリー機能の性能指数であるMR比は,実用的には,数十~100%以上が必要とされているが,これまでのスピンFET研究においては,現行のFETと同じ横型素子が用いられており,MR比は室温では0.1%程度であった。

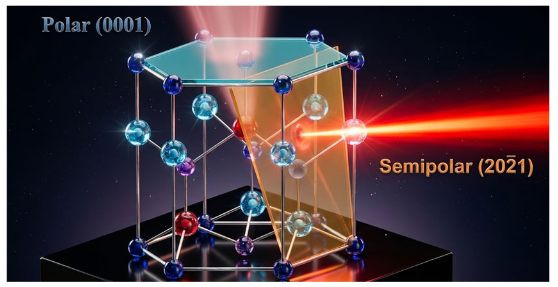

今回,半導体トンネル障壁層材料として酸化物半導体であるGa2O3を用いた。この半導体は,結晶構造が複雑であるため,鉄(Fe)などの一般的な強磁性電極と組み合わせた単結晶TMR素子の作製は困難と考えられていた。そのため,これまでTMR素子のトンネル障壁層としてはほとんど注目されていなかった。

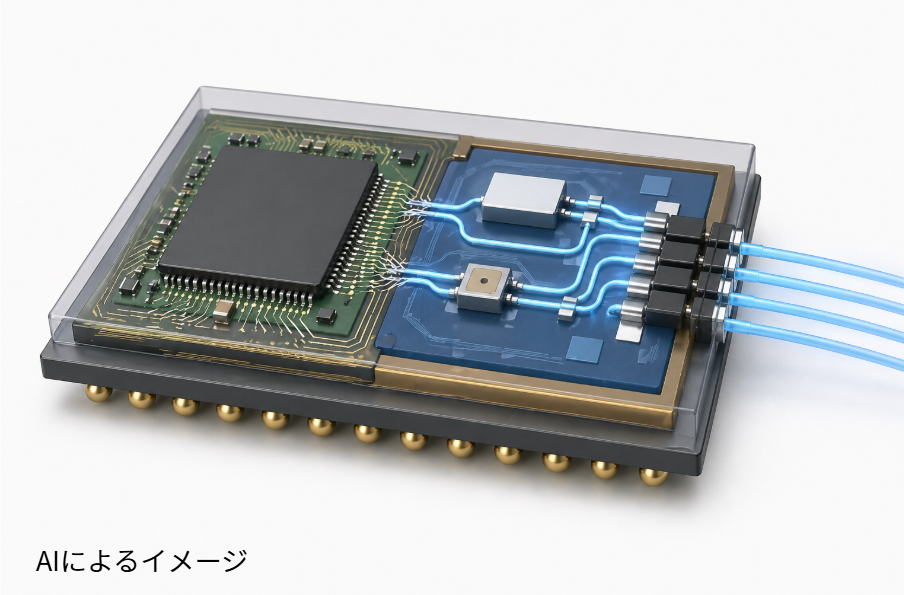

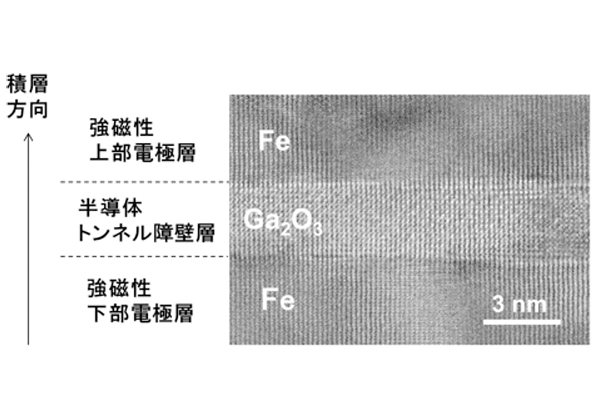

産総研は独自の成膜プロセスを開発して,Fe強磁性電極とGa2O3トンネル障壁層から成る全単結晶TMR素子を作製した。成膜には蒸着の一種である分子線エピタキシー法を用いた。この単結晶Ga2O3膜上には,単結晶Fe上部電極を直接成長させることができる。なお,得られた単結晶Ga2O3膜を詳細に分析したところ,スピネル型という単純な結晶系の構造であった。

Ga2O3層を単結晶化することによりMR比が大幅に増大し,半導体トンネル障壁層の素子としてはこれまでで最も高い値(92%)を示した。MR比の増大は,単結晶MgOを用いたTMR素子と同様に,トンネル障壁層と上部強磁性電極の単結晶化により電子が波の性質を保ったまま伝搬できるようになったためと考えられるという。

今後は,MR比の一層の向上を図ると共に,Ga2O3膜に電界をかけて出力電流を制御するためのゲート構造の設計と動作実証を行ない,5年後を目途に実用的な性能の縦型スピンFETを開発するとしている。これにより,超省電力のノーマリー・オフ・コンピューターの実現に繋がる。

関連記事「京大ら,シリコンを用いたスピントランジスタの室温動作に成功」「東北大,永久/逆永久スピンらせん状態間を制御」「NTTら,電子スピンの長距離輸送に成功」