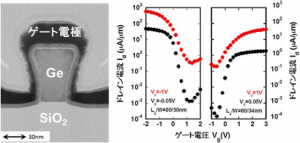

産業技術総合研究所 ナノエレクトロニクス研究部門 連携研究体グリーン・ナノエレクトロニクスセンター特定集中研究専門員の臼田宏治氏らは,大規模集積回路(LSI)の3次元積層技術に向けた多結晶ゲルマニウム(Ge)トランジスタのp型動作とn型動作の両方を実現し,多結晶Ge-CMOSが実現可能であることを示した。

多結晶Geは、広く用いられている多結晶シリコン(Si)に比べ,より低温(500 ℃以下)で形成することができる。そのため,集積回路上に熱的ダメージを与えずにCMOS回路を直接積層することが可能であり,3次元LSIの要素技術として有望視されている。さらに,Ge中の電子と正孔の移動度はSiよりも高いために,高性能化や低電圧動作が期待される。

しかし,p型トランジスタの動作は実現していたが,これまでn型トランジスタの動作報告例はなく,CMOS回路の実現性は不明であった。今回,多結晶Geの結晶品質を向上させることで初めてnMOSFETの動作を実現し,多結晶GeのCMOS化が可能であることを示した。

さらに,pMOSFETでは,単結晶Si-pMOSFETに匹敵する,従来の3倍近い電流駆動力を達成した。これらの成果から,高性能多結晶Ge-CMOSを積層した3次元LSIの実現と,それによるLSIの大幅な小型化と高機能化,低消費電力化が期待される。今後は,多結晶GeのpMOSFETとnMOSFETを組み合わせたCMOS回路を絶縁膜上に形成し,回路動作の実証を目指す。さらに,Geの高い移動度を生かして,単結晶Si-CMOS回路を超える性能を目指す。

詳しくはこちら。