東京工業大学はWOWアライアンスと共同で,直径300mmのシリコンウエハーをデバイス層の半分にも満たない2μm級に超薄化することに成功し,この厚さでは半導体メモリー(DRAM)の特性が劣化する現象を初めて明らかにした(ニュースリリース)。

東京工業大学はWOWアライアンスと共同で,直径300mmのシリコンウエハーをデバイス層の半分にも満たない2μm級に超薄化することに成功し,この厚さでは半導体メモリー(DRAM)の特性が劣化する現象を初めて明らかにした(ニュースリリース)。

半導体メモリーチップを積層し,上下チップを電気接続すれば,積層数に比例したメモリー容量が得られ,極端に微細化しなくても大容量メモリーを得ることができる。上下配線の長さはバンプサイズとチップを貫通する接続孔(TSV)の長さ(チップの厚さ)で決まり,この配線長を短くすれば配線抵抗と電気容量が低減される。

バンプ接続を前提としたこれまでのTSV配線では,チップ厚さの限界が約50μmであり,バンプとTSVを合わせた長さは約100μmになる。TSV一本当たりのデータ転送速度を少なくし(低周波数),帯域幅を高めると消費電力が低くなる。このカギを握るのはウエハーの厚さである。だが,どこまで薄くできるのかはこれまで明らかになっていなかった。

研究グループはウエハーを薄化してから積層し,TSVで直接上下チップを接続配線するバンプレスTSV配線を開発している。この方法を用いれば,バンプが不要になり,薄化プロセスの限界までウエハーを薄くすることができる。FRAM,MPU,DRAMに対して,同研究グループはこれまでに10μm以下の薄化に成功していた。

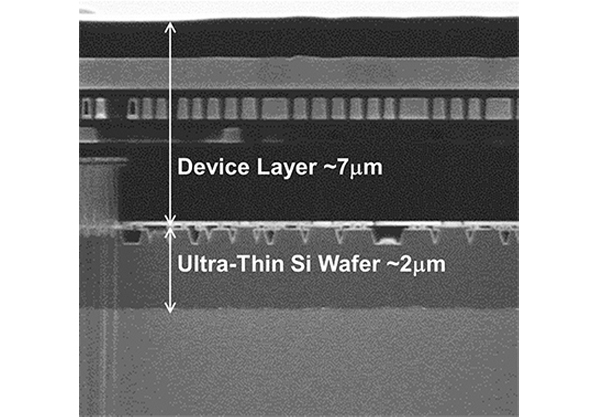

今回はどこまでウエハーを薄くできるかの極限を知るために2μm台の薄化を行なった。この厚さはデバイス層の1/3以下の厚さで,機械研削方式では世界で初めての試み。先端2ギガビットDRAMが形成された300mmウエハーを厚さ775μmから約0.3%の2μmまで薄化した。

このような薄化を行なうことにより,ようやくデバイス特性の劣化が観察され(観察個所の厚さは2.6μm),DRAMの限界厚さが4μm前後にあることを明らかにした。厚さ4μmは,DRAMのデバイス層よりも薄く,可視光も透過する。

この薄化技術を利用すると,デバイス層を含めても10μm以下となり,この厚さがTSVの長さになる。これは従来のバンプを利用したTSVに比べ長さが約1/10に短縮される。TSVが短くなると,これに比例して配線抵抗と電気容量がそれぞれ小さくなる。

長さが1/10になると配線性能の指標となる配線抵抗と電気容量の積は1/100に減少する。このため4ギガビット,8ギガビット,16ギガビットといったメモリー容量の拡大に合わせてWOWプロセスを使って4層,8層,16層積層しても薄化したチップであれば電気的な課題が解消される。

薄化チップを64層積層しても全体の厚さは800μm以下に収まり,仮に16ギガビットメモリーを積層すれば小型ながら1テラビットの大規模メモリーを実現することができる。このようなメモリーの大容量化を従来の微細化で行なっても,ずいぶん先の線幅5nmでも達成できない。このように積層されたDRAMは,FOWLP技術におけるデバイス部品としても用いることができる。

超薄化でTSVを短く,また小さくできると,加工しやすくなり,生産性が大幅に向上する。同時にバンプの制約がなくなるので,1平方mm当たり1000本から1万本のTSVを形成することができる。

ウエハー厚さ4μmで,このようなTSVを利用すれば低周波数でも高帯域が可能となり,ギガビット転送速度当たりのエネルギー効率が向上する。このためビッグデータ向けのサーバーやスマートフォンをはじめ,小型携帯端末の消費電力が大幅に削減される。メニコアMPUと組み合わせれば,テラバイトの高帯域を実現することが可能になるとしている。

関連記事「東工大ら,DRAMを搭載した300mmウエハを厚さ4㎛に超薄化することに成功」「産総研,カーボンナノチューブのインプラントによる新たな配線作製技術を開発」「産総研,多結晶Geによる3次元積層集積回路のための積層CMOSの開発に成功」