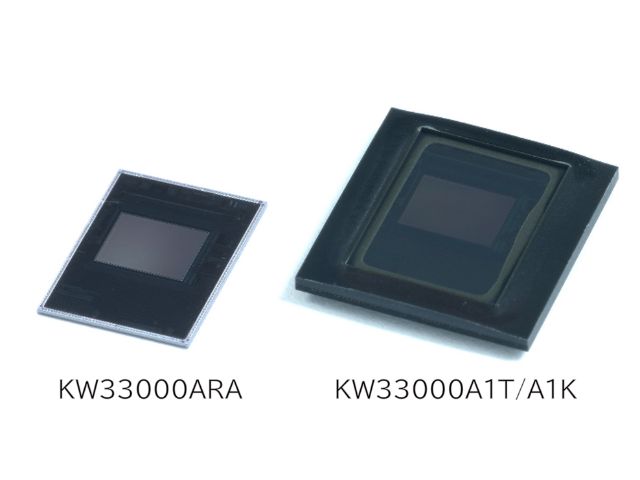

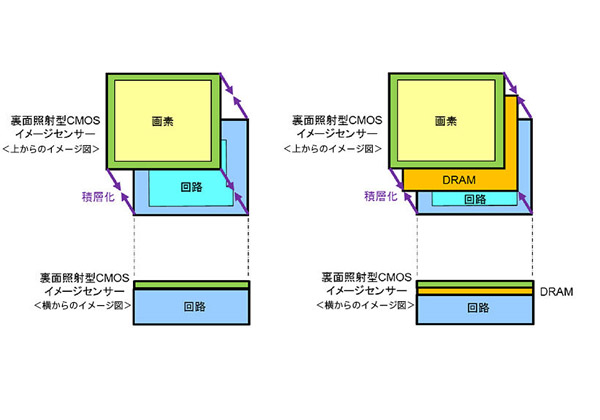

ソニーは,業界で初めてDRAMを積層した3層構造の積層型CMOSイメージセンサーを開発した(ニュースリリース)。これは,従来の裏面照射型画素部分と信号処理回路部分との2層構造の積層型CMOSイメージセンサーに,さらにDRAMを積層したもの。

ソニーは,業界で初めてDRAMを積層した3層構造の積層型CMOSイメージセンサーを開発した(ニュースリリース)。これは,従来の裏面照射型画素部分と信号処理回路部分との2層構造の積層型CMOSイメージセンサーに,さらにDRAMを積層したもの。

DRAMを積層したこの開発品は,高速読み出しを実現し,動きの速い被写体の撮影時にも,フォーカルプレーン歪みを抑えた静止画や,フルHD(1920×1080画素)サイズで毎秒最大1,000フレーム(従来比約8倍)のスーパースローモーション動画の撮影が可能。

高速読み出しを実現するために,画素部分から読み出したアナログ映像信号をデジタル信号へ変換する回路を,従来の2段から4段構造に倍増するなどにより処理能力の向上を図った。

また,イメージセンサーから他のLSIへ信号を出力するインターフェースの規格には速度の制約があるが,開発品ではDRAMを積層し,高速に読み出した信号を一旦DRAMに保存するため,規格に合わせた速度で出力することができる。

その結果,1930万画素サイズの静止画1枚を120分の1秒(従来比約4倍)で読み出すことができる高速撮影を実現した。

さらに,3層にそれぞれ搭載された回路間のノイズの低減など,設計上の技術的な課題を克服しているという。また,同社が長年培ってきた積層型の製造技術や知見などを活用することで,3層化で構造が複雑になっても,高い品質と信頼性を実現しているという。