富士通研究所とソシオネクストは,サーバやスイッチで使用される半導体チップと光モジュール間のデータ通信において,従来と比べて2倍高速となる1チャネル当たり毎秒56Gb/sの通信速度を実現する,世界最小電力の送受信回路を開発した(ニュースリリース)。

富士通研究所とソシオネクストは,サーバやスイッチで使用される半導体チップと光モジュール間のデータ通信において,従来と比べて2倍高速となる1チャネル当たり毎秒56Gb/sの通信速度を実現する,世界最小電力の送受信回路を開発した(ニュースリリース)。

近年,急速に需要が拡大しているクラウドコンピューティングを支えるために,データセンターの処理能力の向上が求められている。データセンターは,スイッチを介して多くのサーバーが接続された大規模なシステムとして構成されており,データセンターの処理能力の向上に伴って,サーバー間でやり取りされるデータ量もますます増加している。

このため,次世代のデータセンターに向けて,サーバーとスイッチ間の光伝送で用いられる光モジュールの通信速度についても現行の2倍に当たる56Gb/sの国際標準化が進んでいる。一方,データセンターにおいては,設備が供給できる電力の制約から,データ送受信回路の電力を増やすことなく通信速度を向上させることが求められている。

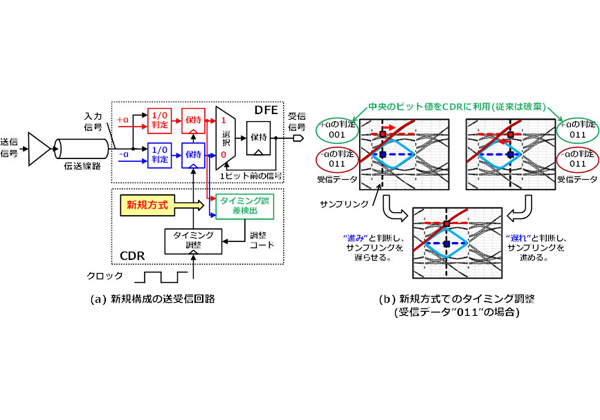

従来の送受信回路においては,劣化した信号を補償する回路であるDFE(Decision Feedback Equalizer)と,入力信号のタイミング誤差を検出する回路であるCDR(Clock and Data Recovery)の占める消費電力が,送受信回路の全消費電力の約3分の2と大きく,これらの消費電力を低減することが課題だった。

DFEは,伝送線路によって劣化した波形を入力として,異なるしきい値+αと-αを持った別々の判定回路でビット値を判定した結果について,1ビット前に処理したビット値が0であれば-α,1であれば+αのしきい値を持った判定回路の結果を選択することで劣化した信号を補償する。CDRは,入力信号を観測することで,入力信号の波形が最大の振幅となった時にDFEが信号を取り込めるように,DFEの動作タイミングを調整する。

今回,CDRの消費電力を削減できる,新たなタイミング誤差検出方式を開発した。DFE演算後の波形を分析した結果,連続する3ビットの入力信号が100または011となる場合において,DFEの2つの判定回路の結果を比較することでDFEの動作タイミングの進み,遅れを検出できることがわかった。これにより,連続する3ビットの入力信号が100または011となるときだけタイミングを検出する,新しいタイミング検出方式を開発した。

開発したタイミング検出方式により,従来必要であったCDRの入力信号のタイミング判定回路を削減でき,加えて,DFEとCDRでタイミングが異なっていたために別途必要だったクロック線などの配線も不要になった。これにより,従来と同じ消費電力で2倍高速となる,56Gb/sの送受信回路の開発に成功した。

この技術により,従来に比べて消費電力を増加させることなくチップと光モジュール間のデータ通信を高速化することができるという。また,光モジュール通信のOIF次期規格にも対応しているため,現行の28Gb/s規格で400Gb/sイーサネットを構築する場合,16個の送受信回路が必要なのに対し,この技術では半分の8個で実現でき,光モジュールの小型化・低電力化も期待される。

今後,両社は,開発した技術をサーバーやスイッチのチップと光モジュール間のインターフェース部などに適用し,2018年度の実用化を目指すとしている。

関連記事「NEDOら,超小型光トランシーバーの実装ボードを開発」「富士通研,MMファイバーの伝送距離を2倍にすることに成功」「富士通,多並列化が可能な光送受信回路を開発」