東北大学の研究グループは,独自技術である超低損傷・中性粒子ビーム技術を用いて「界面準位が1011cm-2eV-1以下の高品質な界面を持ったAlOx/GeOx/Geゲートスタック構造」を作製することに成功した(ニュースリリース)。

東北大学の研究グループは,独自技術である超低損傷・中性粒子ビーム技術を用いて「界面準位が1011cm-2eV-1以下の高品質な界面を持ったAlOx/GeOx/Geゲートスタック構造」を作製することに成功した(ニュースリリース)。

半導体産業においては世界的な競争のもと,新材料の導入や微細化研究が盛んに行なわれている。特にMOSトランジスタは半導体産業の最大の牽引車であり,国際競争を勝ち抜くためには,その高性能化の研究は極めて重要となる。

集積回路の高性能化には回路の微細化が不可欠だが,これまで,微細化した回路素子からのリーク電流による発熱が大きくなりすぎて「技術世代22nm」以降の超高集積回路の実現は難しいとされてきた。

この壁を打ち破るため,チャネル材料にゲルマニウムを用いたMOSトランジスタの開発が精力的に進められている。ゲルマニウムMOSトランジスタにおける製造上および特性上の最大の課題は,「高誘電率膜およびゲルマニウムゲート酸化膜積層(スタック)構造形成時における,ゲルマニウムとゲルマニウム酸化膜の界面準位密度をいかに下げられるか」という点にある。

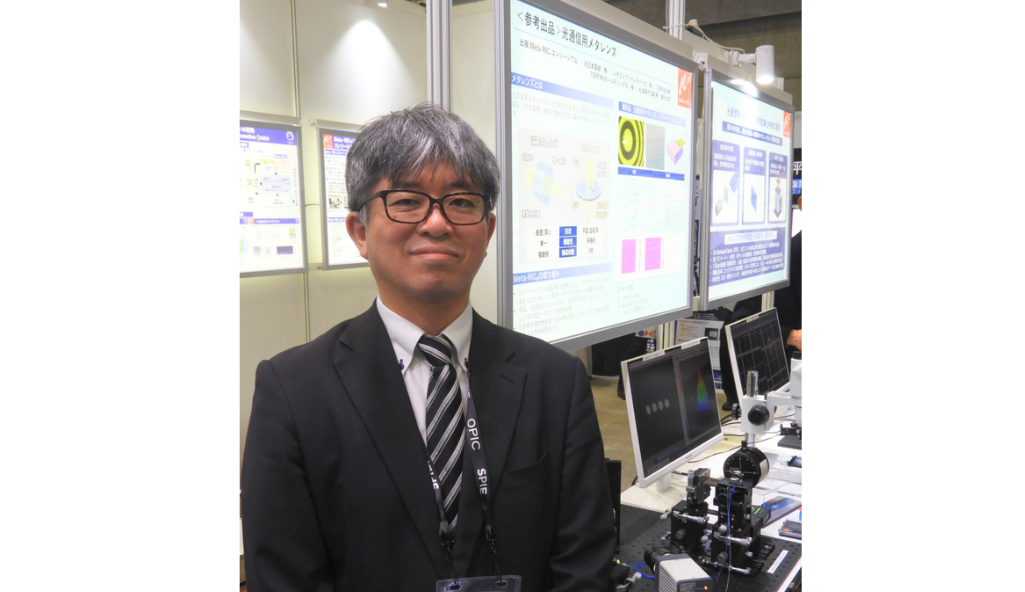

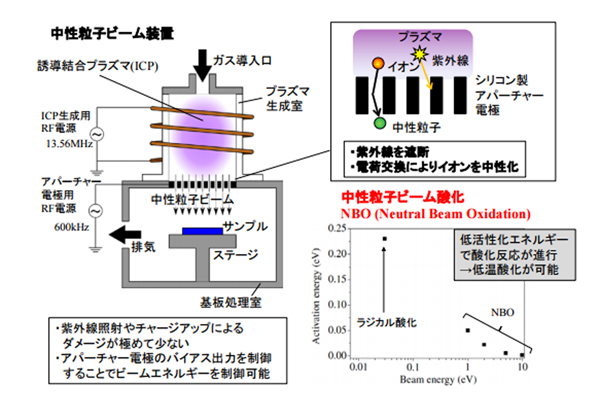

すでに研究グループは「中性粒子ビーム酸化を用いて3次元シリコン構造を無損傷に低温酸化することで,起立型MOSトランジスタにおける電子の移動度を向上させられる」という研究成果を発表している。

今回,研究グループは,ゲルマニウム基板表面の自然酸化膜を除去したのち,アルミニウム蒸着によってカバーされた高品質ゲルマニウム表面に酸素中性粒子ビームによる「300℃以下の低温酸化で均一超低損傷なAlOx(1.5nm)」と「GeO2比率が20~30%程度の高品質ゲルマニウム酸化膜(1nm)」を同時に形成することで,MOSキャパシタ構造試作を行ない,電気的に界面準位を測定した。

その結果,「1011cm-2eV-1 以下という極めて低い界面準位密度の実現」に成功した。これにより,今後ゲルマニウムMOSトランジスタの開発が大きく前進することが期待されるとしている。

研究グループはこの成果について,中性粒子ビームによる加工・表面改質・材料堆積技術は,現在の半導体業界が直面している革新的ナノデバイスの開発を妨げるプロセス損傷を解決する全く新しいプロセス技術であるとしている。

また,この技術を用いた装置はプラズマプロセスとして実績がありもっとも安定した装置において用いられているプラズマ源をそのまま用い,中性化のためのグラファイトグリットを付加するだけで実現できるため,今後,数十nm以下のナノデバイスにおける革新的なプロセスとして実用化されていくことが期待されるとしている。

関連記事「慶大,CMOSプロセスで最高となる光共振器を作製」「キヤノン,APS-Hで約2億5,000万画素のCMOSを開発」「東大,半導体pn接合の界面電場観察に成功」