広島大学らの研究グループは,SOTB-MOSFET(エス・オ・ティ・ビィ-モスフェット)の回路設計用コンパクトトランジスタモデル「HiSIM-SOTB」(ハイシム-エス・オ・ティ・ビィ)が,国際標準に認定されたことを発表した(ニュースリリース)。今回のモデル「HiSIM-SOTB」は,広島大学が産業技術総合研究所などと協力して開発したトランジスタコンパクトモデルで,集積回路の超低消費電力化を実現できるトランジスタとして期待されているSOTB-MOSFETに対応したもの。

広島大学らの研究グループは,SOTB-MOSFET(エス・オ・ティ・ビィ-モスフェット)の回路設計用コンパクトトランジスタモデル「HiSIM-SOTB」(ハイシム-エス・オ・ティ・ビィ)が,国際標準に認定されたことを発表した(ニュースリリース)。今回のモデル「HiSIM-SOTB」は,広島大学が産業技術総合研究所などと協力して開発したトランジスタコンパクトモデルで,集積回路の超低消費電力化を実現できるトランジスタとして期待されているSOTB-MOSFETに対応したもの。

集積回路の低消費電力化には,MOSFETの微細化で漏れ電流が急激に増える短チャネル効果とチャネル内のドーピング原子数の減少による特性ばらつき増大の抑制が大きな課題になっている。その対策として,シリコンチャネル層を極薄化(10nm)すると同時にドーピングしない極薄SOIトランジスタが提唱されていたが,所望の特性を得るために閾値電圧を調整することが困難という問題があったが,それをSOTB-MOSFETが解決した。

シリコンチャネル層の極薄化に加え,下部絶縁体(BOX)層を薄くすることで,特性ばらつきを小さく保ったまま基板ドーピング濃度や基板バイアスの調整で,トランジスタ特性を理想的に調整できる。その結果,0.4Vという低電源電圧動作で電力消費が従来の10分の1程度の集積回路を実現できる。新たに開発されたSOTB-MOSFETを用いた集積回路を設計するには,電源電圧を0.4Vへ大幅に引き下げた場合の回路動作を正確に再現するトランジスタコンパクトモデルが不可欠となる。

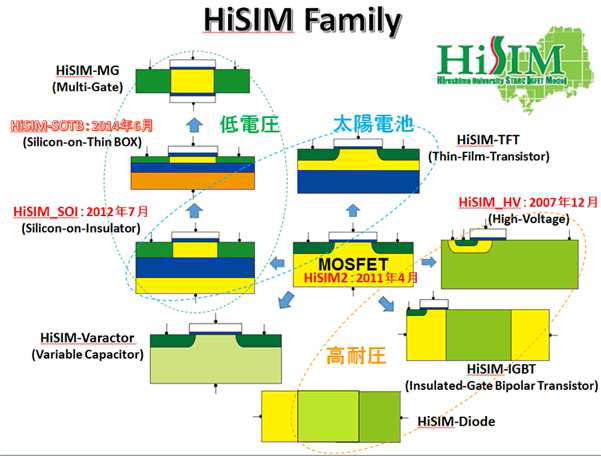

SOTB-MOSFETは構造の自由度が非常に高く,デバイス構造によって特性が敏感に変化するデバイスで,これを正確に記述するには,物理原理に従わないとモデルとして予測性がなくなる。広島大学は,2012年に国際標準に選定されたHiSIM-SOIをあらゆるデバイス構造に適応できるよう大幅に改良し,HiSIM-SOTBを開発した。

HiSIM-SOTBでは,極薄膜SOI(シリコンチャネル層)上部と下部,基板上部の3カ所の表面ポテンシャルをポアソン方程式を解いて正確に求める。そのためには3次のニュートン方程式の数値解を安定に求めるという難問の解決が必要だったが,適切なアルゴリズムを開発した

結果,基板濃度の変更や基板バイアスの印加によるキャリア分布の変化を正確に再現することができた。一方,コンパクトモデルとしての利便性を損なわないよう,差し支えない部分は効率的な近似式を多用し,計算時間を短縮するさまざまな工夫をしている。

SOTB-MOSFETによる集積回路を設計するためには,これまであまり重要と考えられていなかった弱電流領域の複雑な電圧依存性を再現するトランジスタコンパクトモデルが不可欠だが,HiSIM-MOSFETはこの特性を正確に再現することを可能にした。また大規模論理回路やアナログデジタル混載回路のシミュレーションにおいても,安定性と高信頼性が高く評価されているという。

研究チームが限られた期間で標準化に足る完成度まで開発できたのは,産官学それぞれの強みを生かす協力体制を迅速に構築できたことにあるという。あらゆるものがネットでつながる世界(IOT)の実現のためには,超低消費電力のマイコンが必要不可欠だが,この分野を中心に大きな需要が期待されている。研究グループは,今後も産官学の協力体制を築くことで,省エネ半導体分野において国内企業が世界に先行する鍵を握ると期待している。

関連記事「産総研,n型/p型MOSFETを3次元積層したCMOS回路の動作に成功」「産総研,電界効果トランジスタの10万倍の寿命を持つトンネルトランジスタを開発」「東大,超低消費電力トンネル電界効果トランジスタを開発」