JST戦略的創造研究推進事業において,東京大学の研究具グループは,極低電圧での動作が可能な新しい構造のトンネル電界効果トランジスタを開発した(ニュースリリース)。

JST戦略的創造研究推進事業において,東京大学の研究具グループは,極低電圧での動作が可能な新しい構造のトンネル電界効果トランジスタを開発した(ニュースリリース)。

LSIの消費電力を下げるため,LSIチップの論理演算に使われているMOSトランジスタの消費電力の低減,特に電源電圧の低減が課題となっている。しかし,これまでのMOSトランジスタでは,論理演算における信号のオン状態とオフ状態の電流をわずかな電圧変化で切り替えることが原理的にできないため,電源電圧を本質的に下げられなかった。

この問題を解決するため,電子がエネルギー障壁を量子力学的にトンネリングする際のトンネル電流を利用し,これをゲート電極により制御するトンネル電界効果トランジスタ(トンネルFET)が,注目されている。しかし,トンネルFETはまだ研究途上で,電流をわずかな電圧変化で急激に切り替えようとしても,オン電流とオフ電流の差を大きくとることができないという問題があった。

また材料的にも,InGaAsやGaSbなどのIII-V族化合物半導体のヘテロ構造を用いるなど,現在のSi集積回路における半導体技術をそのまま転用することが難しく,短期間での実用化が困難という問題もあった。

トンネルFETにおいて,オン電流とオフ電流の差を大きくとるためには、電子の量子力学的トンネリングを起こすエネルギー障壁幅を非常に薄くすること,さらにこのトンネル電流を大きくすることができる材料上の工夫をすることが必要。

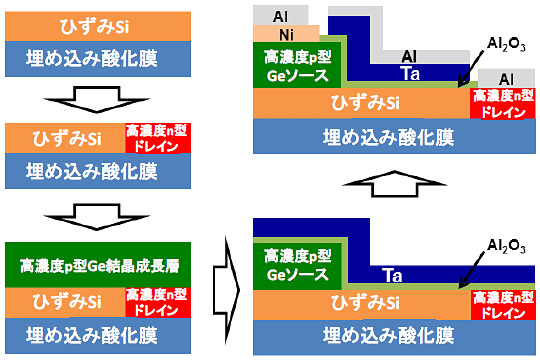

研究グループは,従来からMOSトランジスタのチャネルとして用いられているSiに,引張り応力を加えたひずみSiとGeのヘテロ界面を用い,トンネリングを起こすソース領域を高濃度のGe,チャネル材料をひずみSiとした。

その結果,主流で用いられている横型(プレーナ)構造で,さらに現在の集積回路プロセスに馴染みやすい材料を用いながらも,極めて薄いエネルギー障壁幅を形成することに成功した。これにより,良好な電界効果トランジスタ特性を示すとともに,わずかな電圧変化で急激に電流を切り替えることと,大きなオン電流とオフ電流の比を得ることの両方を同時に実現することに成功した。

加えて,今回のトンネルFETの基板側に電圧を加えることにより,トンネルFETのオン電流が大きく向上できることも見いだした。結果として,S係数と呼ばれる電流変化の早さの尺度で,最小値28mV/decade,またオン電流とオフ電流の比が107以上というこれまでのトンネルFETで最も大きい値を実現した。この素子により,現行トランジスタの0.9から0.3ボルト(V)以下にまで、電源電圧を低下しても動作する集積回路を実現する道を開いた。

トンネルFET技術は,これまで半導体分野の進展を支えてきた素子寸法の微細化に頼ることなく低消費電力化が実現できるため,近い将来限界を迎えると言われている素子微細化の課題を解決し,特に日本の今後の半導体産業の活性化と再生につながるキーデバイス技術となる可能性を秘めている。

また,製品応用の観点では,センサネットワークや無給電で動作する集積回路などを含め,極低消費電力素子が必要な分野はすでに多く存在している。研究具グループは,トンネルFETの実用化により,これまでの半導体集積回路技術では実現できなかった新たな応用分野や市場が出現し,応用領域がより一層広がっていくことと期待している。

関連記事「産総研,立体型トランジスタの低周波ノイズを1/5に低減することに成功」「東芝ら,超低消費電力マイコン向けに2種類のトンネル電界効果トランジスタを開発」「京大ら,シリコンを用いたスピントランジスタの室温動作に成功」「産総研,微細トランジスタの不純物濃度分布を高精度で測定するシミュレーション技術を開発」