富士通研究所とFujitsu Laboratories of America, Inc.は,次世代サーバに搭載されるCPUなどのチップ間データ通信を行う送受信回路において,消費電力を2割削減可能なクロック伝送技術を開発した。現在,CPUなどのチップ間でのデータ通信速度の高速化に伴い,通信を行なう送受信回路に含まれるクロック伝送回路の消費電力が増大しており,低消費電力化が求められていた。

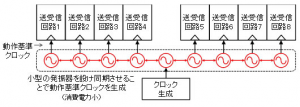

これは,各送受信回路に小型の発振回路を搭載し,各発振器を同期させることで従来のクロック伝送回路を不要とし,低電力化を実現した伝送方式。すべての動作基準クロック(発振器出力)は,クロック生成出力に同期するように制御される。その結果,各送受信回路への動作基準クロックの周波数と位相は,クロック生成出力の周波数と位相と一致する。同期をとるための各発振器間の信号は,従来のクロック信号を伝送する場合に比べ小振幅な信号のため低電力化が可能となる。

同期化を実現するにあたり,隣接した発振器出力の振幅差に比例した小振幅な信号を各発振器にフィードバックする。振幅差がゼロになるようフィードバックがかかるため,最終的には振幅差はゼロになり,各発振器の出力クロックの周波数と位相は一致する。すべての隣接した発振器が接続されており,かつ,その1つがクロック生成回路に接続されているため,すべての発振器はクロック生成出力に同期するよう動作する。このようにして,小振幅な差信号を生成,伝送することにより,複数の同期したクロックを生成することができる

詳しくはこちら。