産業技術総合研究所ナノエレクトロニクス研究部門 連携研究体グリーン・ナノエレクトロニクスセンター特定集中研究専門員の鎌田善己氏らは,大規模集積回路の3次元積層技術に向けた多結晶ゲルマニウム(Ge)トランジスタが5桁を超えるオン・オフ比を示すことを実証した。

LSIの高性能化・低消費電力化は微細化に依ってきたが,これ以上は困難となってきている。一方,複数のLSIを積層し,上下のLSI間にTSVやマイクロバンプを導入するなど,3次元的な集積回路を形成する研究開発も進められているが,TSVやマイクロバンプは,現状では配線ピッチが必ずしも十分でなく,高コストであるといった問題点があるため,新たな3次元積層技術が求められている。

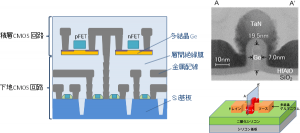

これらの問題点を解決するためには,配線を含む集積回路を連続的に多層に形成できる技術(積層CMOS技術)が有望と考えられ,産総研では,多結晶Geが低温で絶縁膜上に形成可能であることに着目し,多結晶Geによる積層CMOSの開発を開始した。

液晶ディスプレーなどで用いられている多結晶シリコン(Si)トランジスタに比べ,多結晶Geトランジスタは,より低温で形成することができ,さらに移動度が高いために,高性能化および低電圧動作が期待される。

今回,トランジスタ構造を微細なフィン型トランジスタとすることで,実用レベルに迫る5桁を超えるオン・オフ比を実現した。これによりスパッタリング成膜やシンプルな製造工程の採用による低コスト化の可能性があり,TSVやマイクロバンプなどを用いたチップ積層による3次元化技術を代替,あるいは補完する新たな3次元積層技術として期待される。

詳しくはこちら。