産業技術総合研究所(産総研)は,立体型トランジスタ(フィンFET)の低周波ノイズをこれまでの最小レベルに低減する技術の開発を行なった(ニュースリリース)。

産業技術総合研究所(産総研)は,立体型トランジスタ(フィンFET)の低周波ノイズをこれまでの最小レベルに低減する技術の開発を行なった(ニュースリリース)。

シリコン集積回路は,その最小構成単位であるトランジスタを微細化することにより高性能化・低コスト化を実現してきた。しかしながらアナログ回路は,デジタル回路に比べ,低周波ノイズの影響を大きく受けてしまうという問題を抱えている。

この低周波ノイズは,トランジスタを微細にするほど増加するため,ノイズの影響を受けずに微細化が進んでいるデジタル回路に対して,アナログ回路においてはより大きなトランジスタを使用する必要があり,コスト削減につながるチップ面積縮小と高性能化の障害になっていた。このため,アナログ集積回路向けのトランジスタにおいてノイズを格段に低減させる技術が強く求められている。

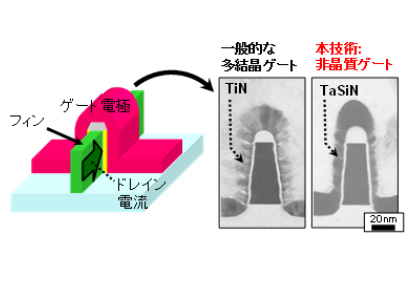

研究グループは,特性ばらつきの抑制に有効である非晶質金属ゲートをフィンFETに導入することにより,通常の多結晶金属ゲート電極を用いる場合に比べ,低周波ノイズを劇的に低減させることに成功した。フィンFETのゲート電極は,一般的に多結晶金属が使用されている。

今回,多結晶金属である窒化チタン(TiN)ゲート電極を持つフィンFETに加え,非晶質金属である窒化タンタルシリコン(TaSiN)をゲート電極に使用したフィンFETを作製した。研究グループは,非晶質金属ゲートを用いることで,トランジスタの動作を決める重要なパラメータであるしきい値電圧や相互コンダクタンスのばらつきが劇的に低減できることを既に発見していおり,今回はトランジスタのドレイン電流に生じるノイズレベルの測定と比較を行なった。

その結果,多結晶金属ゲート電極においては顕著なノイズが観測されたが,非晶質金属ゲート電極においてはノイズの振幅が非常に小さく抑えられることが分かった。顕著なノイズが観測された多結晶金属ゲート電極の場合、フリッカノイズ特有の周波数に反比例する特性を示している。一方、非晶質ゲート電極では、周波数に反比例する特性を示すフリッカノイズが顕著に抑制されていることが分かった。

今回達成された低周波ノイズの抑制効果を,これまで一般的に集積回路に使用されてきたバルクプレーナ型トランジスタ,フィンFET同様に低ばらつきである特長をもつSOIプレーナ型トランジスタと比較した結果,非晶質金属ゲートフィンFETは,他のトランジスタ構造に比べても約5分の1程度(0.21倍)までノイズが抑制されていることが分かった。

このようなノイズ抑制効果が得られると,アナログ集積回路のチップ面積を5分の1まで縮小してもノイズ増加を引き起こすことがなく,集積回路のコスト低減のメリットをもたらすと期待されるという。また,0.21倍の面積縮小はゲート長を約半分に縮小できることに相当し,ノイズの増加を引き起こすことなく,さらに高速動作が可能なトランジスタをアナログ回路で利用できるようになる。

研究グループは波及効果として,スマートフォンやタブレット等の高性能な無線端末の低コスト化や,現状よりも高い周波数動作が必要な次世代高速無線通信の普及促進が期待できるとしている。

関連記事「東大,超低消費電力トンネル電界効果トランジスタを開発」「東芝ら,超低消費電力マイコン向けに2種類のトンネル電界効果トランジスタを開発」「京大ら,シリコンを用いたスピントランジスタの室温動作に成功」「産総研,微細トランジスタの不純物濃度分布を高精度で測定するシミュレーション技術を開発」