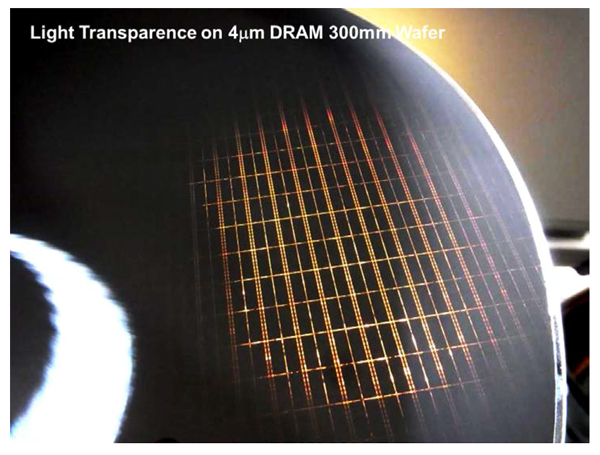

東京工業大学,ディスコ,富士通研究所,PEZY Computing,WOWアライアンス(東工大を中心とする産学アライアンス)と共同で,半導体メモリ(DRAM)が搭載された直径300mmシリコンウエハの厚さを4µmまで超薄化する技術を開発した(プレスリリース)。

東京工業大学,ディスコ,富士通研究所,PEZY Computing,WOWアライアンス(東工大を中心とする産学アライアンス)と共同で,半導体メモリ(DRAM)が搭載された直径300mmシリコンウエハの厚さを4µmまで超薄化する技術を開発した(プレスリリース)。

この技術はバンプ(電極部にメッキで形成した配線接続のための突起)を用いないWOW積層技術(ウエハーの積層(Wafer-on-Wafer)で大規模集積回路を作製する三次元集積技術)を利用して,シリコンウエハの厚さをデバイス層より薄い4µmまで薄化することに成功したもの。

半導体メモリチップを積層し,上下チップを電気接続すれば,積層数に比例したメモリ容量が得られ,極端に微細化しなくても大容量メモリを得ることができる。このとき,上下配線の長さは,バンプサイズとチップを貫通する接続孔(TSV)の長さ(チップの厚さ)で決まり,これまでのTSV配線では,チップ厚さの限界が約50μmであり,バンプとTSVを合わせた長さは約100μmになった。

研究グループは,ウエハを薄化してから積層し,TSVで直接上下チップを接続配線するバンプレスTSV配線を開発している。この方法を用いれば,バンプが不要になり,薄化プロセスの限界までウエハを薄くすることができる。

同薄化技術を利用すると,デバイス層を含めても10μm以下となり,この厚さがTSVの長さになる。これは従来のバンプを利用したTSVに比べ長さが約1/10に短縮される。TSVが短くなると,これに比例して配線抵抗と電気容量がそれぞれ小さくなる。長さが1/10になると配線性能の指標となる配線抵抗と電気容量の積は1/100に減少する。

薄化チップを16層しても全体の厚さは200μm以下に収まり,仮に16ギガビットメモリを積層すれば小型ながら256ギガビットの大規模メモリを実現することができる。これをわずか4個配置するだけでテラビットメモリを実現することができる。このような大規模メモリ容量を従来方法で達成しようとすると,10nm,7nm級の微細化が必要になる。

研究グループは,薄化前と薄化した後のリフレッシュ時間の累積故障率が変わらないことを確認し,薄化による新たな原子欠陥が生じないことを実証した。この技術が実用化すれば,ビッグデータ向けのサーバーやスマートフォンをはじめ小型携帯端末の消費電力が大幅に削減される。また,メニコアMPUと組み合わせれば,テラバイトの高帯域を実現することが可能になる。