産業技術総合研究所(産総研)は,大規模集積回路(LSI)の消費電力低減に有効な,インジウムガリウムヒ素(InGaAs)n型MOSFET(nMOSFET)とシリコンゲルマニウム(SiGe)p型MOSFET(pMOSFET)により構成される3次元積層CMOSリングオシレータ回路を試作し,その回路動作に成功した。

産業技術総合研究所(産総研)は,大規模集積回路(LSI)の消費電力低減に有効な,インジウムガリウムヒ素(InGaAs)n型MOSFET(nMOSFET)とシリコンゲルマニウム(SiGe)p型MOSFET(pMOSFET)により構成される3次元積層CMOSリングオシレータ回路を試作し,その回路動作に成功した。

ポストシリコン材料と呼ばれるInGaAsやSiGeは,従来のLSIで用いられているシリコン(Si)に比べ,より低電圧で多くの電流を流すことができる。そのため,これらのポストシリコン材料を組み合わせたデュアルチャネルCMOS回路は,高速性などの性能を維持したままで,大幅な消費電力低減が期待できる。

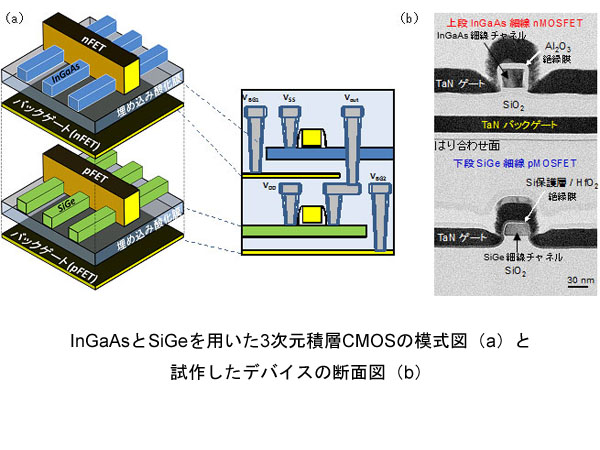

InGaAs-nMOSFETとSiGe-pMOSFETを絶縁膜上に幅30 nm程度の細線チャネルで形成し,細線チャネル型MOSFETを作製した。精密な3次元積層化により上下のMOSFETは10 nm程度の精度で位置合わせされ,回路面積の縮小化と近接配線による高性能化が期待される。

具体的には,SiGeの細線チャネルを,SiGeを高温で熱酸化する酸化濃縮法により形成し,チャネル表面のGe組成を70%以上とした。一方,InGaAsの細線チャネルは,SiGe-pMOSFETの作製後,InGaAs層をはり合わせ,エッチング加工して形成した。

また,InGaAs-nMOSFETの下部に形成されたTaNバックゲート層は,InGaAs層をはり合わせる前に,SiGe-pMOSFET上に絶縁膜を介して堆積させた。これら上下段のMOSFETを配線することにより,CMOS回路を作製した。

今回開発したInGaAsとSiGeを用いた3次元積層CMOSインバータを用いて,代表的なダイナミックデジタル回路であるCMOSリングオシレータを試作したところ,電源電圧0.37 Vという低電圧でのリングオシレータ動作を確認した。これはインバータ伝達特性が良好で,素子間の特性が均一なことによると考えられる。また,−20 Vのバックゲート電圧をかけると,発振周波数が増加することが確認された。

研究グループは今後もポストシリコン材料を用いた3次元積層CMOSの開発を進めるほか,はり合わせ技術を応用して,これまでシリコンでは困難であった発光や受光デバイスなどと3次元集積し,LSIとポストシリコンデバイスをワンチップ化した,多機能集積化デバイスの開発を目指す。