1.はじめに

1.1光アイソレータ

光アイソレータは,順方向の信号光を透過し逆方向の戻り光を遮断する非相反な光素子である。半導体レーザーにわずかでも戻り光が再入射すると発振波長の揺らぎや線幅の増加が起こり,さらに戻り光のレベルが高くなると副モードの増加や光強度の変動などが起こり,通信品質に深刻な悪影響を及ぼす。そのため,送信モジュールの出力端に光アイソレータを配置することが一般的である。バルク型の光アイソレータはイットリウム鉄ガーネット(Y3Fe5O12 ,YIG)系の磁気光学結晶から構成され,ファラデー効果により光ビームに対して非相反な偏波回転を与えることで動作する。しかし,シリコンフォトニクスのような光集積回路内に組み込む場合は,シリコン導波路をベースとした光アイソレータの実現が望まれる。今後は,半導体レーザーばかりでなく半導体光増幅器(SOA)も光集積回路に組み込まれるケースが増えると予想され,SOAと反射点間の共振モードの抑制や逆方向の自然放出光の除去など光アイソレータの集積に関する需要は高まっていくと考えられる。

1.2磁気光学結晶集積の課題

光通信波長帯(1.3 ~ 1.55 μm)で大きなファラデー効果を示すのは,Yの一部をBi やCeで置換したBi:YIGやCe:YIGである。これらはガドリニウムガリウムガーネット(Gd3Ga5O12,GGG)の格子定数を調整したSGGGウエハ上に結晶成長することで得られる。しかし,シリコンやIII-V族化合物半導体などとは結晶構造や格子定数が大きく異なり,結晶成長ができない。

YIGをアモルファス状態でシリコン基板上に堆積しアニーリングによって結晶化した後,そのYIG膜を種層としてCe:YIGの多結晶膜を形成する手法が開発されている。しかし,アニーリングで800℃程度の高温プロセスが必要である点が課題である。化合物半導体プロセスでは成長温度以上であり,シリコンCMOSのバックエンドプロセスや後工程では許容されるサーマルバジェットを越えて金属配線層などに悪影響を及ぼす。そこで,局所的な加熱が可能なレーザーアニーリングが検討されているが,まだシリコン導波路上で結晶化し光アイソレータを作製した報告はない。

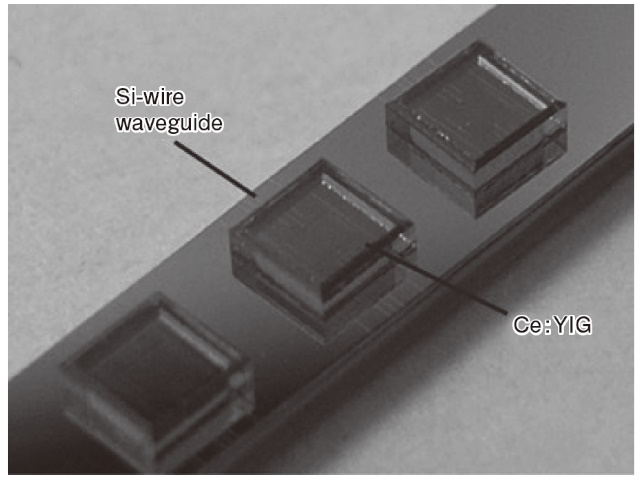

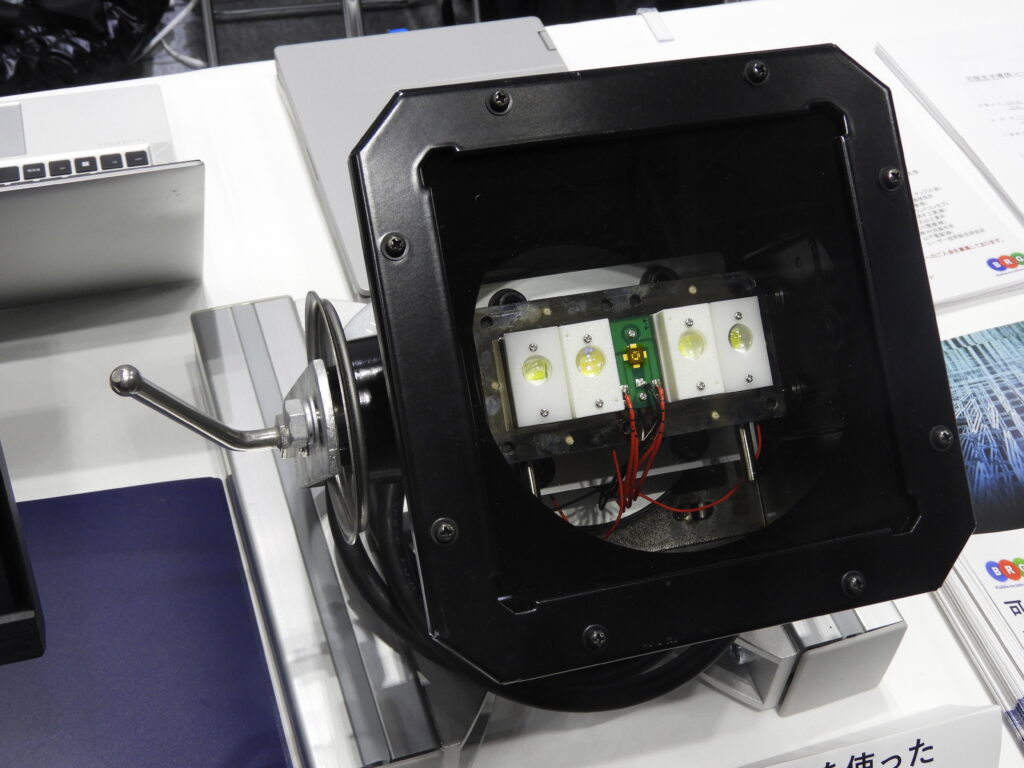

執筆者らは,異種材料集積技術のひとつであるプラズマ表面処理による直接接合を用いてCe:YIGのシリコン導波路上への集積技術を開発している。200℃程度の比較的低温の加熱処理で接合が得られるため,バックエンドプロセスや後工程で問題なく用いることができる。SGGGウエハ上に成長した良質なCe:YIG結晶が利用でき,高い磁気光学特性が得られる。図1に,1.5 mm角に切り出したCe:YIG/SGGG小片をシリコン光回路上に貼り付けたサンプルの写真を示す。小片に切り出すことにより異種材料集積で課題になりやすい熱膨張係数差による応力を軽減できる。

1.3低損失化の課題

光アイソレータはパッシブな光素子であり,レーザーやSOAへの投入電力の増加を避けるためにも低損失であることが強く求められる。前節で述べた直接接合法で光アイソレータを作製した場合,次の二点が過剰損失の要因になる。一つは,TMモード伝搬による伝搬損失である。平面導波路構造では位相不整合によりファラデー効果が得られないため,「非相反移相効果」と呼ばれる磁気光学効果を利用する。非相反移相効果は磁気光学結晶を上部に積層した導波路構造ではTMモードにのみ発現する。シリコンフォトニクスで標準的な導波路の高さ220 nmでは大きな非相反移相効果が得られる反面,Ce:YIGへの染み出しが大きいためCe:YIGの光吸収による伝搬損失が大きくなる。光アイソレータの動作に必要な非相反位相シフタの長さはおよそ0.3 ~ 0.4 mmであるのに対し,ハンドリングの関係上1.5 mmという余分な領域を接合していることで過剰損失になっている。もう一つの要因は,接合した小片境界における急峻な屈折率変化に起因した散乱損失である。高さ220 nmの導波路におけるTMモードの電磁界は縦方向に大きく分布するため,片端で3 dB以上の大きな散乱損失を生んでいる。これまでに実証したマッハツェンダー干渉計型光アイソレータでは挿入損失が13.5 dBとなっていた。

【月刊OPTRONICS掲載記事】続きを読みたい方は下記のリンクより月刊誌をご購入ください。

本号の購入はこちら