豊橋技術科学大学と米マサチューセッツ工科大学の研究グループは,磁性絶縁膜中のストレスと,磁石の波であるスピン波の関係を解明し,これらをうまく使うと,実用化の期待されているスピン波演算素子を小型化できることを示した(ニュースリリース)。

豊橋技術科学大学と米マサチューセッツ工科大学の研究グループは,磁性絶縁膜中のストレスと,磁石の波であるスピン波の関係を解明し,これらをうまく使うと,実用化の期待されているスピン波演算素子を小型化できることを示した(ニュースリリース)。

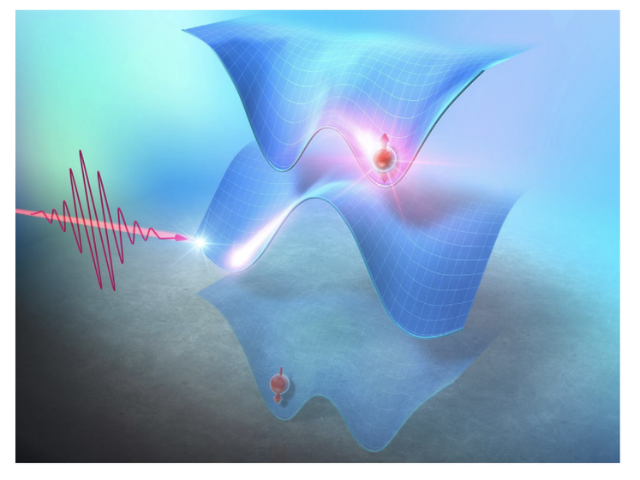

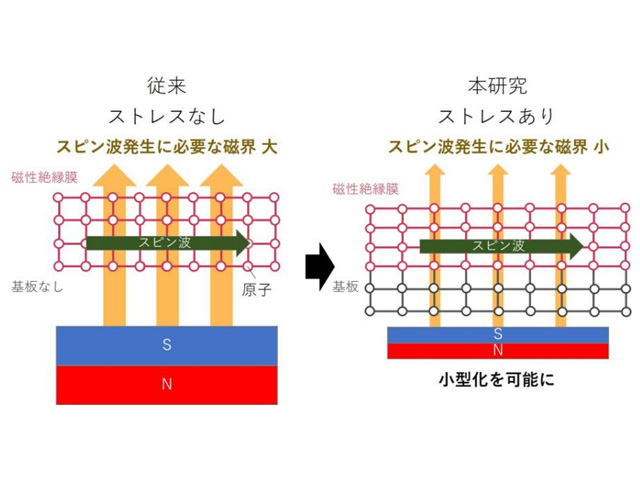

近年の半導体材料を利用した電子デバイスは,高集積化によって,チップの温度が高くなり,不具合を起こすなどして,急成長する情報化社会からの要求に答えることが難しくなってきている。そこで,電子自体は移動せずスピンだけを伝えることで,情報処理を行ない,熱の発生が極めて抑えられるスピン波集積回路の開発が注目を集めている。

この中でも,磁性絶縁膜を伝わるスピン波は,エネルギーの損失が小さく,長距離伝送が可能という利点をもつ。その一方で,磁性絶縁膜中でスピン波を伝えるには,磁性絶縁膜に比較的大きな永久磁石部品を付属する必要があり,スピン波集積回路実現に向けた課題となっていた。

今回の研究では,YIGと同じガーネット構造を持つ,格子定数の異なる3つのガーネット基板上に,パルスレーザー堆積法を用いて,厚さ約100nmのYIG薄膜を形成し,結晶構造と結晶ひずみ,およびストレスの大きさを調べた。

作製したYIG上に,電子線描画プロセスを用いてスピン波を励起・検出するための電極1対を形成し,外部磁界とスピン波の伝搬周波数の関係を測定した。結晶ひずみによる磁気異方性の変化を含んだスピン波の分散関係式を計算し,測定結果と概ね一致することを確認した。また,生じるひずみの大きさを変えることで,ひずみの無い状態と比べて,スピン波の励起に必要な磁石のサイズを約2.5倍小さくできた。

これによりスピン波集積回路全体が小型にでき,デバイスのチップ化が可能になった。今後は,この手法のスピン波の多入出力位相干渉素子,実際のスピン波デバイスへ適用し,まず,チップ化されたスピン波集積回路の機能のデモンストレーションを目指すとしている。