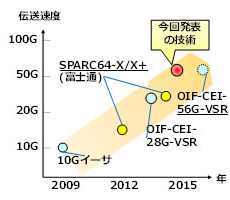

富士通研究所は,次世代サーバに搭載されるCPUなどのチップ間データ通信において,世界最高速である毎秒56Gb/sの高速データを受信可能な受信回路を開発した(プレスリリース)。

富士通研究所は,次世代サーバに搭載されるCPUなどのチップ間データ通信において,世界最高速である毎秒56Gb/sの高速データを受信可能な受信回路を開発した(プレスリリース)。

近年,サーバのデータ処理能力を向上させるため,CPUの高性能化とともに,CPUなどのチップ間のデータ通信速度の高速化が求められている。具体的には,次世代の高性能サーバに向け,現行の2倍の高速化に当たる56Gb/sの通信速度への期待が高まっていおり,筐体間の光伝送などで用いられる光モジュールの通信速度についても,OIFにて56Gb/sの標準化が進んでいる。

受信時に劣化した信号波形を補正する回路の処理能力向上として,劣化した入力信号波形を補償する回路であるDFEの処理能力向上が有効。DFEの基本的な考え方は,1ビット前のビット値に応じた入力信号を補正し入力信号の変化を強調するというもの。56Gb/sの通常の回路設計でDFEは16個を連結させて使用するが,タイミングエラーの問題があった。

同社は,受信信号の品質劣化を補償する回路に対して,新たなアーキテクチャである先読み回路を適用し,並列処理を実現して回路の動作周波数を高め,従来の2倍となる56Gb/sで動作する受信回路の開発に成功した。

この技術により,次世代サーバやスーパーコンピュータなどの高性能化が期待される。同社では開発した技術をCPUや光モジュールのインタフェース部などに適用し,2016年度の実用化を目指す。さらに,次世代サーバやスーパーコンピュータなどの製品への適用も検討していく。