東京工業大学大学院理工学研究科教授の松澤昭氏と,同准教授の岡田健一氏らの研究グループは,ディジタル回路で構成する新方式のクロック生成回路の作製に成功した。

発振器が注入信号に同期して発振をおこす「注入同期現象」を安定的に利用し,フィードフォワード制御による位相同期を行うなことにより実現した。従来のクロック生成回路は,帰還(フィードバック)制御による正確な位相同期が必要なため,ディジタル回路では構成できなかった。

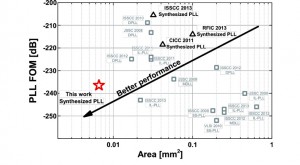

最小加工寸法65nmのシリコンCMOS プロセスで試作した新型クロック発生回路は,0.4G~1.4GHzのクロックを生成可能であり,0.9GHz 出力時の消費電力は0.78mW と非常に低い。さらに の極小寸法(0.0066mm2)で実現した。

クロック生成回路は,ほぼすべての集積回路に内蔵されており,新方式のクロック生成回路を使えば,身のまわりのあらゆる機器に超小型バッテリーレスセンサを組み込むことが可能となる。

詳しくはこちら。